电子工程技术丛书

# 高速电路 设计实践

Practice of High Speed Circuit Design

● 王剑宇 苏 颖 编著

电子工业出版社

PUBLISHING HOUSE OF ELECTRONICS INDUSTRY

# 高速电路设计实践

## Practice of High Speed Circuit Design

本书作者长期从事高速电路设计开发工作，从实践中精选出六十多个经典案例，总结出两百多项设计要点，精心编著成此书，希望帮助读者成为高速电路设计领域的“高手”。

上架建议：计算机 / 硬件电路设计 · EDA

策划编辑：赵丽松

责任编辑：毕军志

封面设计：徐海燕

本书贴有激光防伪标志，凡没有防伪标志者，属盗版图书。

ISBN 978-7-121-10131-1

9 787121 101311 >

定价：42.00 元

电子工程技术丛书

# 高速电路设计实践

王剑宇 苏 颖 编著

電子工業出版社

Publishing House of Electronics Industry

北京 · BEIJING

## 内 容 简 介

本书从设计实践的角度出发，介绍了在从事高速电路设计的工作中需要掌握的各项技术技能，并结合工作中的具体案例，强化了设计中的各项要点。

在本书的编写过程中，作者避免了纯理论的讲述，而是结合设计实例叙述经验，将复杂的高速电路设计，用通俗易懂的语言陈述给读者。本书覆盖了高速电路设计所涉及的常用技术，适用于电子设计专业的高年级学生，以及从事电路开发、测试的硬件工程师。

未经许可，不得以任何方式复制或抄袭本书之部分或全部内容。

版权所有，侵权必究。

## 图书在版编目（CIP）数据

高速电路设计实践/王剑宇，苏颖编著. —北京：电子工业出版社，2010.2

(电子工程技术丛书)

ISBN 978-7-121-10131-1

I. 高… II. ①王…②苏… III. 印刷电路—电路设计 IV. TN410.2

中国版本图书馆 CIP 数据核字（2009）第 236816 号

策划编辑：赵丽松

责任编辑：毕军志

印 刷：北京丰源印刷厂

装 订：三河市万和装订厂

出版发行：电子工业出版社

北京市海淀区万寿路 173 信箱 邮编 100036

开 本：787×1 092 1/16 印张：18.25 字数：467.2 千字

印 次：2010 年 2 月第 1 次印刷

印 数：4 000 册 定价：42.00 元

凡所购买电子工业出版社图书有缺损问题，请向购买书店调换。若书店售缺，请与本社发行部联系，

联系及邮购电话：(010) 88254888。

质量投诉请发邮件至 zlts@phei.com.cn，盗版侵权举报请发邮件至 dbqq@phei.com.cn。

服务热线：(010) 88258888。

# 前　　言

在万兆以太网、数据中心、高性能传输网络等技术的推动下，电路的设计趋于高速化。

目前市场上与高速电路设计相关的书籍很多，但是很难找到由第一线工程师编写的、立足于实践，以讨论高速设计为题材，结合实际工作中的案例，并加以辅助分析的书籍。本书作者长期在业界著名公司从事第一线的高速电路设计开发工作，积累了大量的设计经验，从实践中精选出六十多个经典案例，总结出两百多项设计要点，精心编著成本书，希望通过本书，对业界朋友有所帮助。

本书最大的特色是完全根源于设计实践，基本不对复杂理论和公式进行讨论，从实际工作的需要出发，将设计中所需要考虑的要点配合案例，翔实地展现在读者面前。

从参考文献列表可知，本书参考的绝大多数文献均来自器件资料，而电子设计工程师在选型和设计的过程中，面对最多的同样也是器件资料。在本书中，作者对设计要点的探讨，均围绕实际工作中常用的器件而展开，以便于增强“实践性”，避免给读者造成云里雾里的感觉。

对于高速电路的初学者而言，即使拥有很好的理论知识，但在实际项目面前，却往往感觉无从入手。以最简单的电容为例，在实际设计中，设计者们都知道容值的选择很重要，但往往容易忽略同样重要的因素，如工作温度、工作电压、封装形式，以及电容类型和成本，等等。小小的电容，最后可能是大问题的罪魁祸首，比如作者曾经遇到电路上某高速芯片工作不稳定，大量调试后发现芯片电源纹波较大，而纹波大的原因是给芯片供电的电源的去耦电容类型不对，将该电容的类型从 Y5V 替换为 X7R，问题就解决了。所以，对于缺乏经验的初入门者，在设计阶段因不知道应考虑哪些因素或不能全面考虑各个因素而使设计存在大量潜在的缺陷，在调试阶段又因不知道故障的本质原因而无从入手。设计的质量当然无法得到保证。

在高速电路设计领域，真正的高手能在电路设计中做到一版成功，减少失误，节省研发费用。那么高手们是如何锻炼而成的呢？一方面需要自己的勤奋实践，另一方面更需要有“秘籍”。希望本书能成为高手们手中的一本秘籍。

全书分 8 章。

第 1 章从设计实例出发，讨论了高速电路与低速电路的区别，高速电路设计中需要着重考虑的要点，并简单介绍了硬件开发的流程以及原理图设计的要点。

第 2 章介绍了在高速电路设计中电阻、电容、电感、磁珠等器件的应用。

第 3 章介绍了逻辑器件的选型，并详细讨论了对 LVDS、LVPECL、CML 等高速电平的应用。

第 4 章介绍了电源设计的要点，结合实例，讨论了对 LDO、DC/DC 电源电路的应用，这一章还简单介绍了电源架构、电源管理、保险管选型等方面的内容。

第 5 章介绍了高速电路设计中时序的分析和设计方法。

第 6 章介绍了复位电路与时钟电路的应用及设计方法。

第 7 章对高速电路设计中常用的 SDRAM、DDR SDRAM、DDR2 SDRAM、ZBT

SRAM、QDRII SRAM、Flash、EEPROM 等存储器件的应用做了详细的介绍。

第 8 章介绍了 PCB 设计中层叠结构与阻抗的计算、信号完整性、电源完整性、EMC、防护、结构与易用性、散热、可测试性等方面的内容。

全书主体内容由王剑宇编写。在本书的编写过程中，查阅了大量的英文资料（参见参考文献列表），由苏颖负责对这些资料进行整理和翻译，同时，苏颖还负责对全书文字和插图的编辑。全书由王剑宇统稿。

高速电路设计是一个不断发展的领域，作者也在不断学习的过程中，因此必然有不少新技术无法反映在本书中，同时，由于作者技术水平和实践能力有限，书中错误之处难免，敬请读者批评指正。

本书从构思到编写完成，历时一年有余，融合的却是作者多年工作的教训、心得和体会。本书反馈邮箱为：[highspeeddesign@yahoo.cn](mailto:highspeeddesign@yahoo.cn)，真诚地希望得到来自读者的宝贵意见和建议。

在本书的编写过程中，参考了大量的中外文资料，同时，在作者技术领域的成长过程中，得到了众多同事、朋友的大力帮助，在此，向这些资料的作者以及同事、朋友们表示真诚的感谢。由于日常工作繁忙，本书的编写只能利用业余时间完成，在生活上，父母给予了理解和大力支持，特此向他们表示衷心的谢意。

王剑宇，苏颖

2009 年 10 月

# 目 录

|                                                       |    |

|-------------------------------------------------------|----|

| 第 1 章 概述 .....                                        | 1  |

| 1.1 低速设计和高速设计的例子 .....                                | 1  |

| 【案例 1-1】 简化的存储电路模块 .....                              | 1  |

| 1.1.1 低速设计 .....                                      | 1  |

| 1.1.2 高速设计 .....                                      | 2  |

| 1.2 如何区分高速和低速 .....                                   | 3  |

| 1.3 硬件设计流程 .....                                      | 5  |

| 1.3.1 需求分析 .....                                      | 6  |

| 1.3.2 概要设计 .....                                      | 7  |

| 1.3.3 详细设计 .....                                      | 7  |

| 1.3.4 调试 .....                                        | 9  |

| 1.3.5 测试 .....                                        | 9  |

| 1.3.6 转产 .....                                        | 10 |

| 1.4 原理图设计 .....                                       | 11 |

| 第 2 章 高速电路中的电阻、电容、电感和磁珠的选型及应用 .....                   | 13 |

| 2.1 电阻的应用 .....                                       | 13 |

| 2.1.1 与电阻相关的经典案例 .....                                | 13 |

| 【案例 2-1】 串联电阻过大，导致板间告警失败 .....                        | 13 |

| 【案例 2-2】 电阻额定功率不够造成的单板潜在缺陷 .....                      | 14 |

| 【案例 2-3】 电阻在时序设计中的妙用 .....                            | 15 |

| 2.1.2 电阻应用要点 .....                                    | 16 |

| 2.2 电容的选型及应用 .....                                    | 17 |

| 2.2.1 与电容相关的经典案例 .....                                | 17 |

| 【案例 2-4】 电容失效导致低温下硬盘停止工作 .....                        | 17 |

| 【案例 2-5】 多次带电插拔子板导致母板上钽电容损坏 .....                     | 18 |

| 【案例 2-6】 高速电路中电容应用问题导致 CPU 工作不稳定 .....                | 18 |

| 2.2.2 高速电路设计中电容的作用及分析 .....                           | 19 |

| 【案例 2-7】 交流耦合电容选择不当引起数据帧出错 .....                      | 20 |

| 【案例 2-8】 利用 0612 封装的电容增强滤波性能 .....                    | 21 |

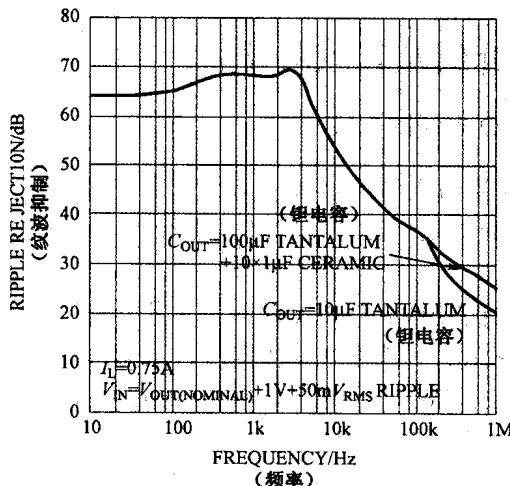

| 【案例 2-9】 LDO 电源应用中的滤波电容 ESR 问题 .....                  | 22 |

| 【案例 2-10】 高频电路中 $1\mu F + 0.01\mu F$ 是否能展宽低阻抗频带 ..... | 24 |

| 2.2.3 高速电路设计常用电容及其应用要点 .....                          | 26 |

| 【案例 2-11】 陶瓷电容选型错误导致单板丢数据包 .....                      | 27 |

|                                          |           |

|------------------------------------------|-----------|

| 【案例 2-12】 根据电路要求进行钽电容选型 .....            | 29        |

| 2.2.4 去耦电容和旁路电容 .....                    | 31        |

| 2.3 电感的选型及应用 .....                       | 32        |

| 2.3.1 与电感相关的经典案例 .....                   | 32        |

| 【案例 2-13】 LC 低通滤波导致输出电源电压纹波偏大 .....      | 32        |

| 【案例 2-14】 大电流通路 PI 型滤波造成电压衰减 .....       | 33        |

| 2.3.2 高速电路设计中电感的作用 .....                 | 35        |

| 2.3.3 高速电路设计常用电感及其应用要点 .....             | 36        |

| 2.4 磁珠的选型及应用 .....                       | 39        |

| 2.4.1 磁珠的滤波机理 .....                      | 39        |

| 2.4.2 高速电路设计中磁珠的选型及其应用要点 .....           | 40        |

| 【案例 2-15】 误用磁珠造成过流保护电路失效 .....           | 41        |

| 2.4.3 磁珠和电感的比较 .....                     | 42        |

| <b>第 3 章 高速电路中的逻辑器件选型及高速逻辑电平应用 .....</b> | <b>44</b> |

| 3.1 与逻辑器件相关的经典案例 .....                   | 44        |

| 【案例 3-1】 逻辑器件输入端上拉太弱造成带电插拔监测功能失效 .....   | 44        |

| 3.2 逻辑器件应用要点 .....                       | 47        |

| 3.2.1 逻辑器件概要 .....                       | 47        |

| 【案例 3-2】 逻辑器件驱动能力过强造成信号振铃 .....          | 51        |

| 【案例 3-3】 同一型号逻辑器件的差异性造成 PHY 配置错误 .....   | 51        |

| 3.2.2 逻辑器件参数介绍 .....                     | 52        |

| 3.2.3 逻辑器件功耗计算 .....                     | 60        |

| 3.2.4 逻辑器件热插拔功能介绍 .....                  | 62        |

| 3.2.5 逻辑器件使用中注意事项的总结 .....               | 68        |

| 3.3 高速逻辑电平应用 .....                       | 68        |

| 3.3.1 高速逻辑电平概述 .....                     | 68        |

| 【案例 3-4】 差分对走线附近信号分布不均衡造成电磁辐射 .....      | 70        |

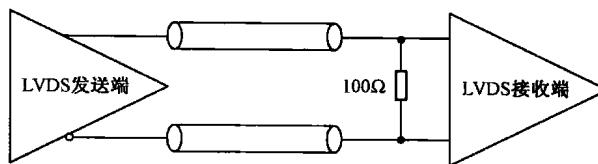

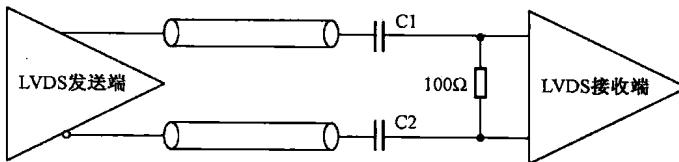

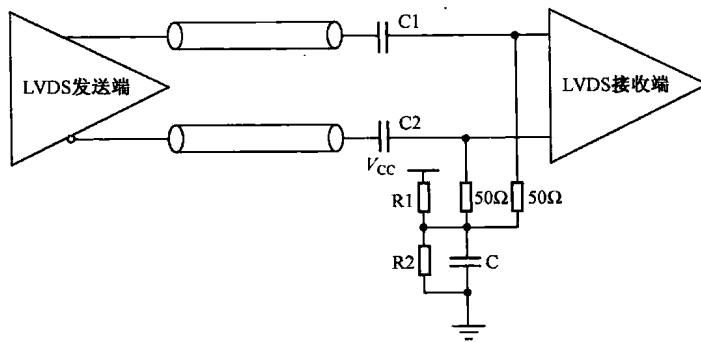

| 3.3.2 LVDS 逻辑电平介绍及其应用要点 .....            | 71        |

| 【案例 3-5】 空闲输入引脚处理有误导致 FPGA 检测到错误输入 ..... | 73        |

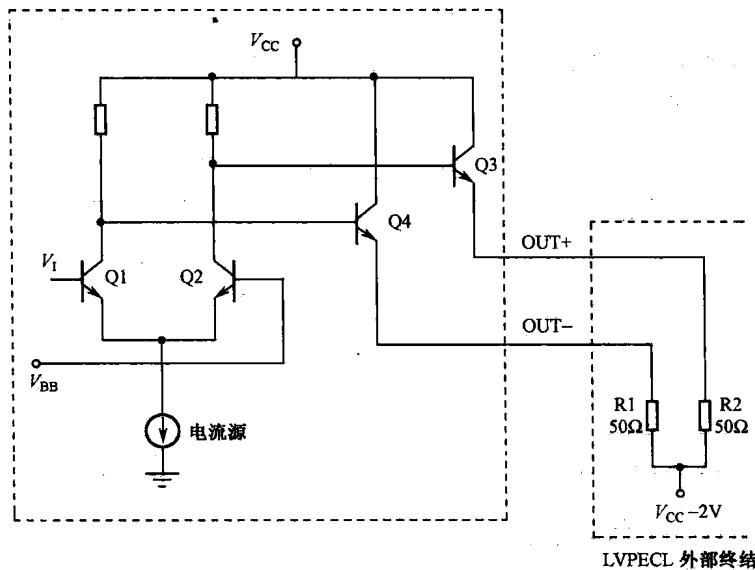

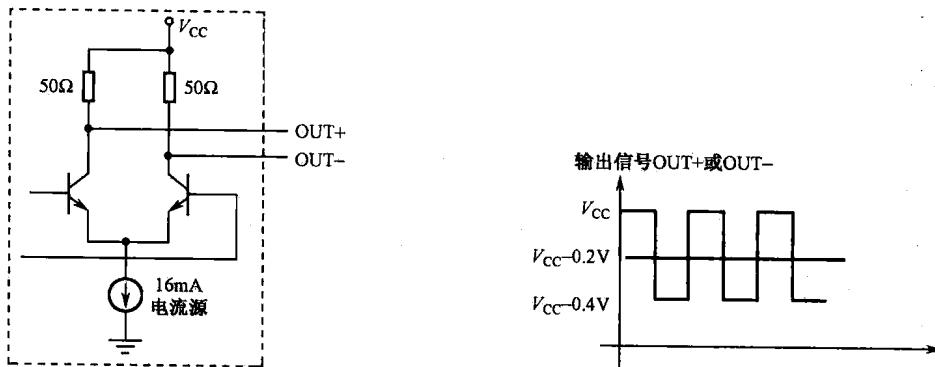

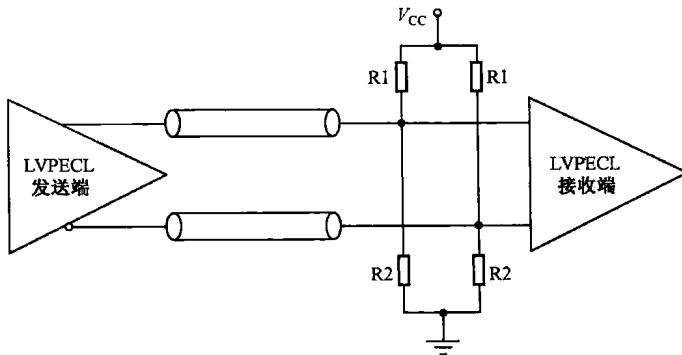

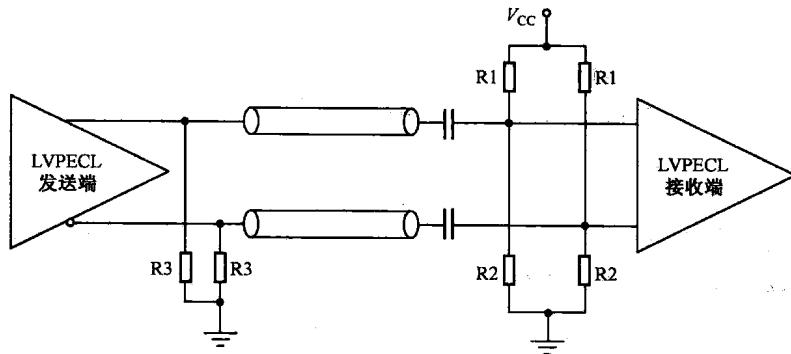

| 3.3.3 LVPECL 逻辑电平介绍及其应用要点 .....          | 75        |

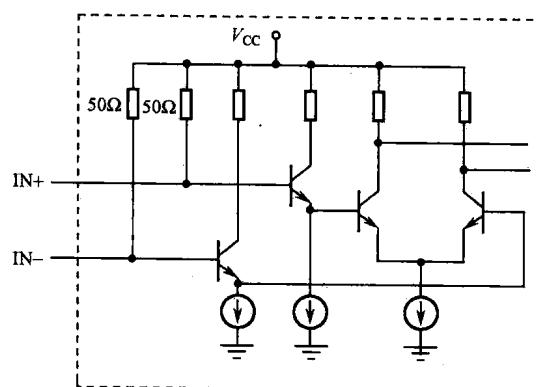

| 3.3.4 CML 逻辑电平介绍及其应用要点 .....             | 77        |

| 3.3.5 高速逻辑电平的比较 .....                    | 78        |

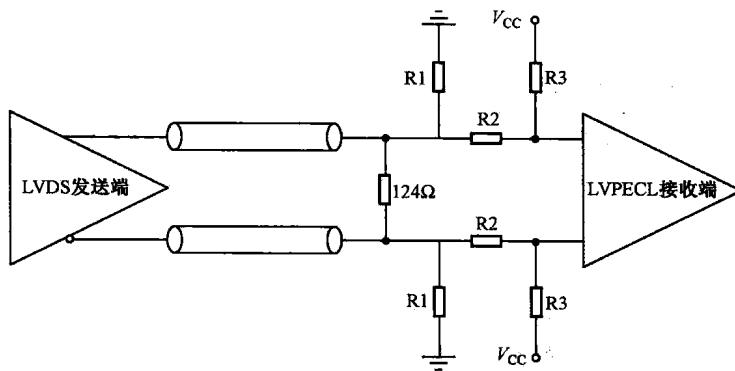

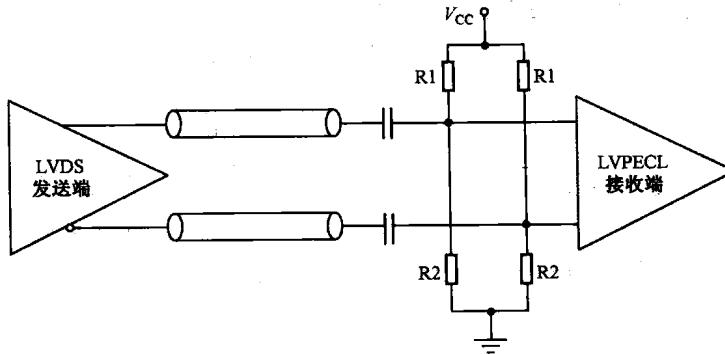

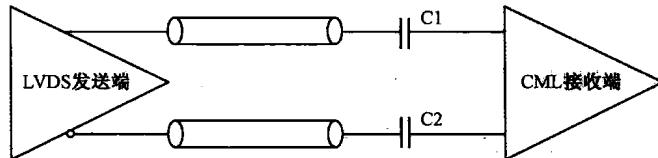

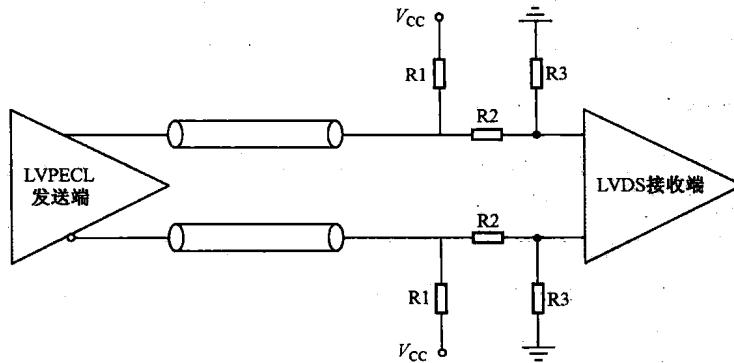

| 3.3.6 高速逻辑电平的互连及其应用要点 .....              | 78        |

| <b>第 4 章 高速电路中的电源设计 .....</b>            | <b>87</b> |

| 4.1 与电源相关的经典案例 .....                     | 87        |

| 【案例 4-1】 LDO 输出电源电平低于设置值 .....           | 87        |

| 【案例 4-2】 电源芯片欠压保护电路导致上电时序不满足设计的要求 .....  | 88        |

| 【案例 4-3】 多电源模块并联工作时的均压措施 .....           | 89        |

|                                        |            |

|----------------------------------------|------------|

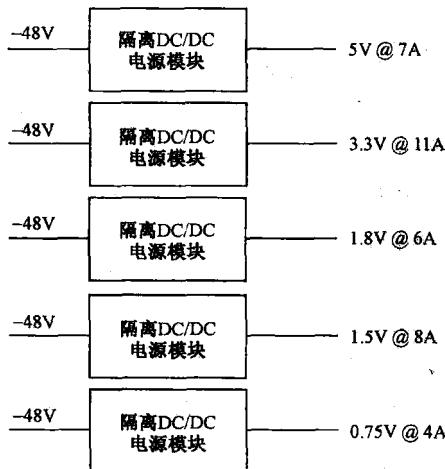

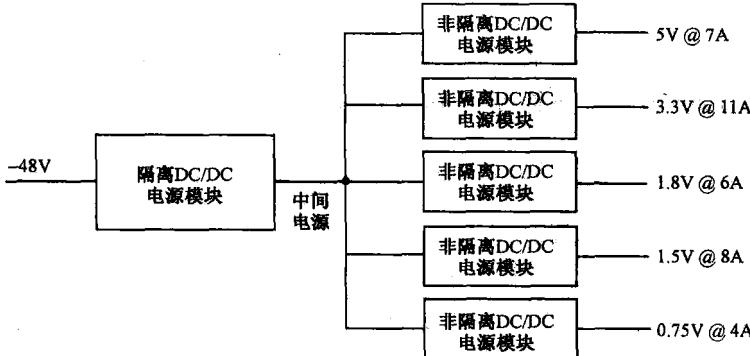

| 4.2 高速电路设计的电源架构 .....                  | 90         |

| 4.2.1 集中式电源架构 .....                    | 90         |

| 4.2.2 分布式电源架构 .....                    | 90         |

| 4.3 高速电路电源分类及其应用要点 .....               | 91         |

| 4.3.1 LDO 电源介绍及其应用要点 .....             | 92         |

| 【案例 4-4】 计算 LDO 工作时的结温 .....           | 95         |

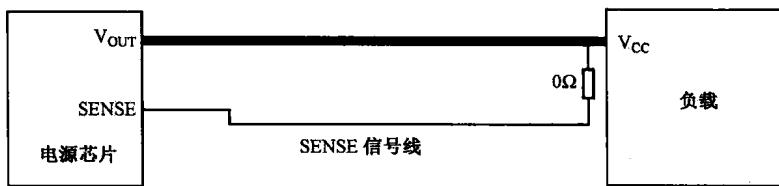

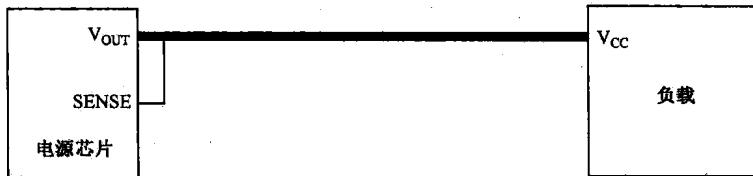

| 【案例 4-5】 SENSE 功能导致电源芯片输出电压不稳定 .....   | 97         |

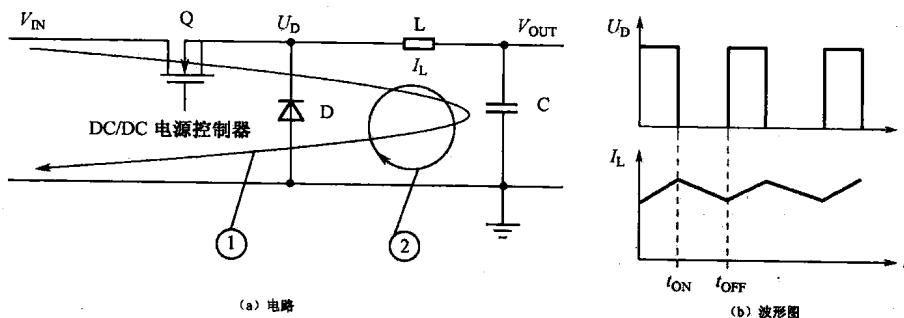

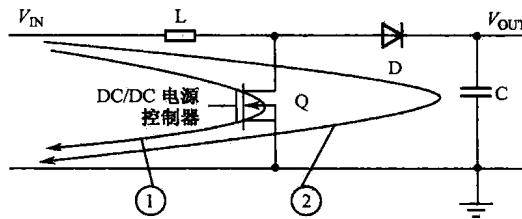

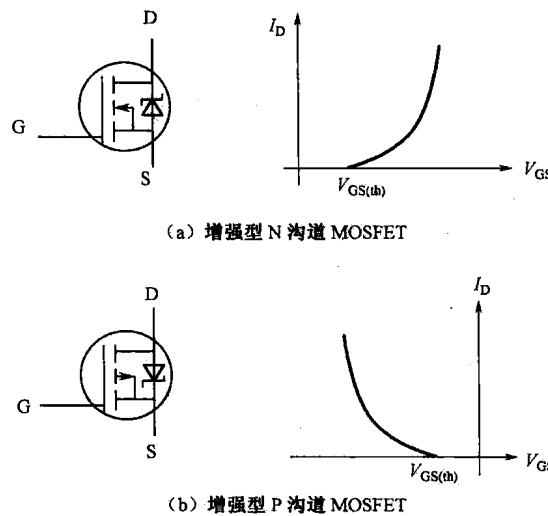

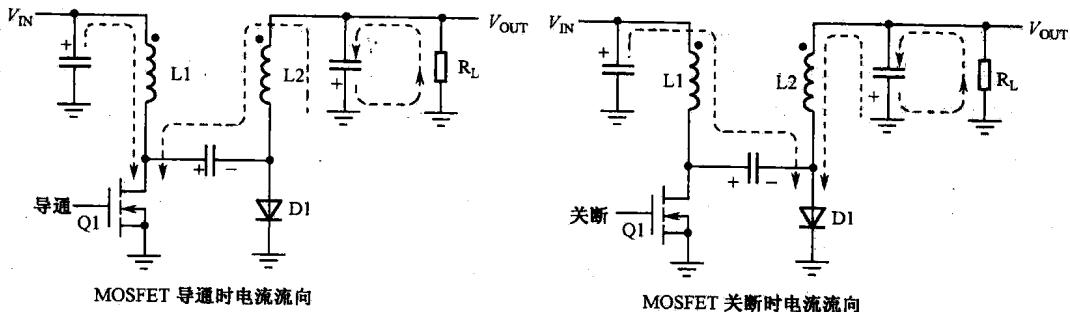

| 4.3.2 DC/DC 电源介绍及其应用要点 .....           | 100        |

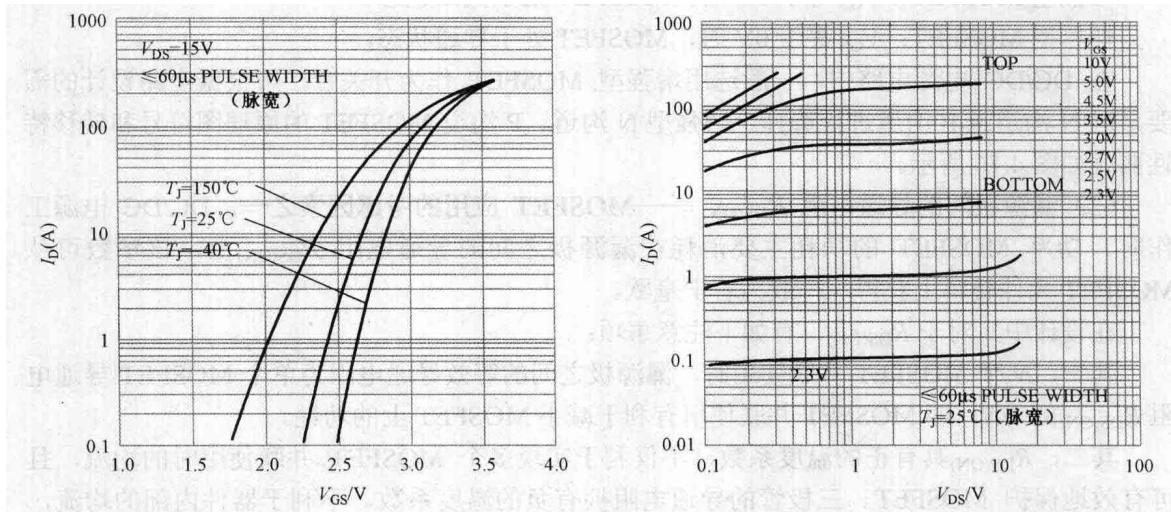

| 【案例 4-6】 计算栅极电流 .....                  | 105        |

| 【案例 4-7】 MOSFET 同时导通导致 MOSFET 损坏 ..... | 108        |

| 【案例 4-8】 -48V 缓启电路中 MOSFET 烧坏 .....    | 111        |

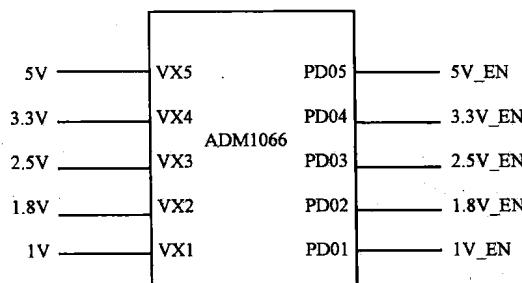

| 【案例 4-9】 基于 ADM1066 对多路电源实现监控 .....    | 114        |

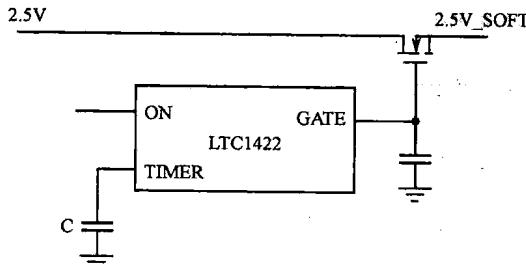

| 【案例 4-10】 基于 LTC1422 实现上电速度的控制 .....   | 115        |

| 【案例 4-11】 基于电源芯片实现上电速度的控制 .....        | 115        |

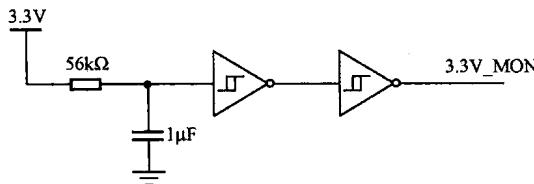

| 【案例 4-12】 基于 RC 阻容电路实现延时功能 .....       | 116        |

| 【案例 4-13】 上电电流过大引起电感啸叫 .....           | 116        |

| 【案例 4-14】 输入电源上电过缓造成输出电源上电波形不单调 .....  | 117        |

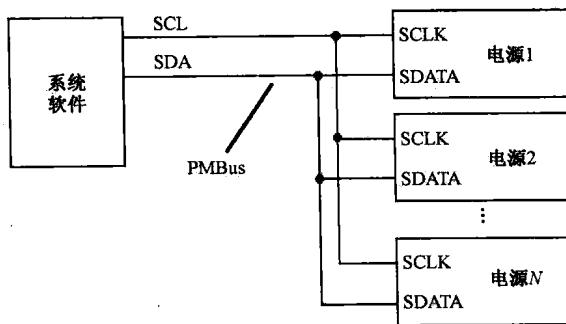

| 4.3.3 电源管理 .....                       | 124        |

| 4.3.4 保险管的选型及应用 .....                  | 124        |

| 【案例 4-15】 热插拔单板的保险管选型 .....            | 126        |

| <b>第 5 章 高速电路中的时序设计 .....</b>          | <b>127</b> |

| 5.1 时序设计概述 .....                       | 127        |

| 5.2 时序参数介绍 .....                       | 127        |

| 5.3 源同步系统时序设计 .....                    | 129        |

| 5.3.1 源同步系统时序设计原理 .....                | 129        |

| 5.3.2 源同步系统时序设计范例一 .....               | 131        |

| 5.3.3 源同步系统时序设计范例二 .....               | 134        |

| 5.4 共同时钟系统时序设计 .....                   | 136        |

| 5.5 源同步系统与共同时钟系统的比较 .....              | 137        |

| <b>第 6 章 高速电路中的复位、时钟设计 .....</b>       | <b>139</b> |

| 6.1 复位电路设计 .....                       | 139        |

| 6.1.1 与复位电路相关的经典案例 .....               | 139        |

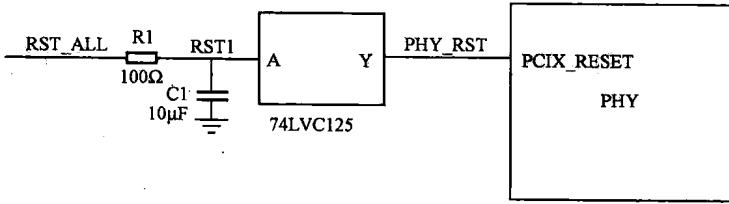

| 【案例 6-1】 主控板无法通过 PCI-X 总线查询到接口板 .....  | 139        |

| 6.1.2 复位设计介绍及其应用要点 .....               | 141        |

| 【案例 6-2】 存储模块读取的错误 .....               | 141        |

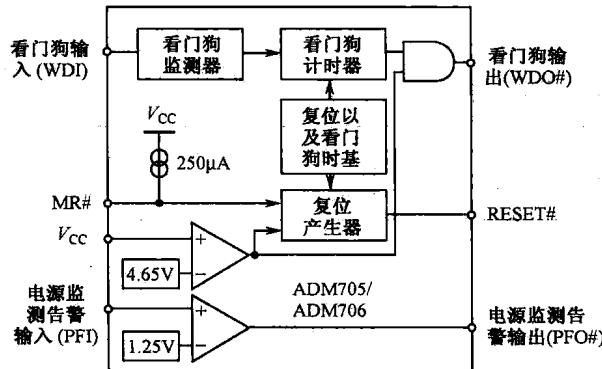

| 6.1.3 专用复位芯片的使用 .....                  | 142        |

| 6.2 时钟电路设计 .....                       | 145        |

| 6.2.1 与时钟电路相关的经典案例 .....               | 145        |

|                                              |            |

|----------------------------------------------|------------|

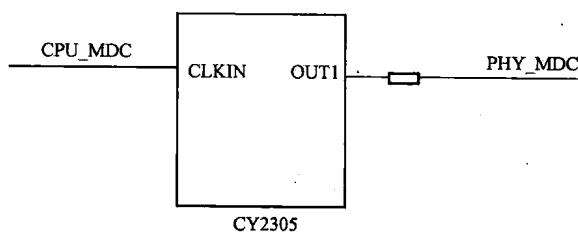

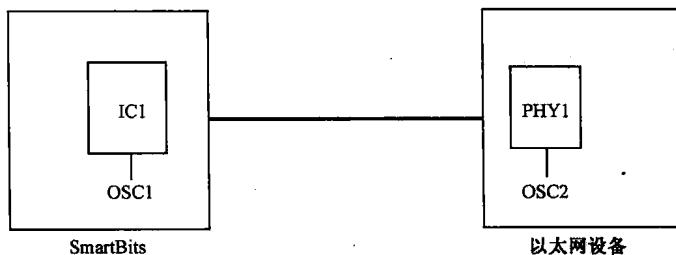

| 【案例 6-3】 系统时钟偏快的问题                           | 145        |

| 【案例 6-4】 PHY 寄存器无法读取的问题                      | 147        |

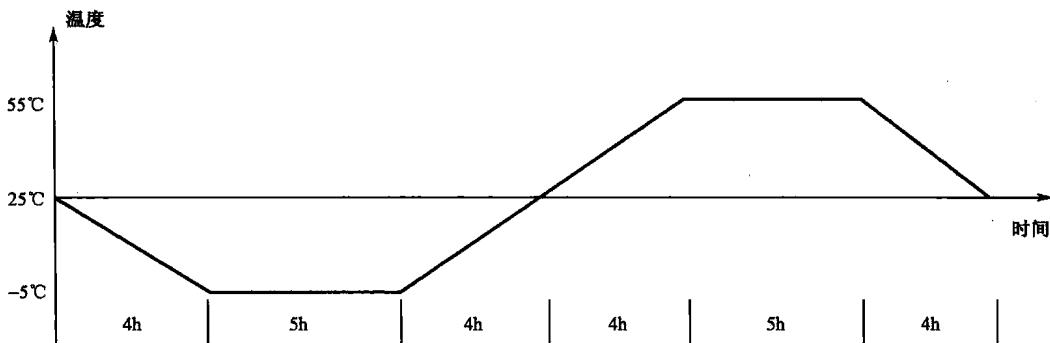

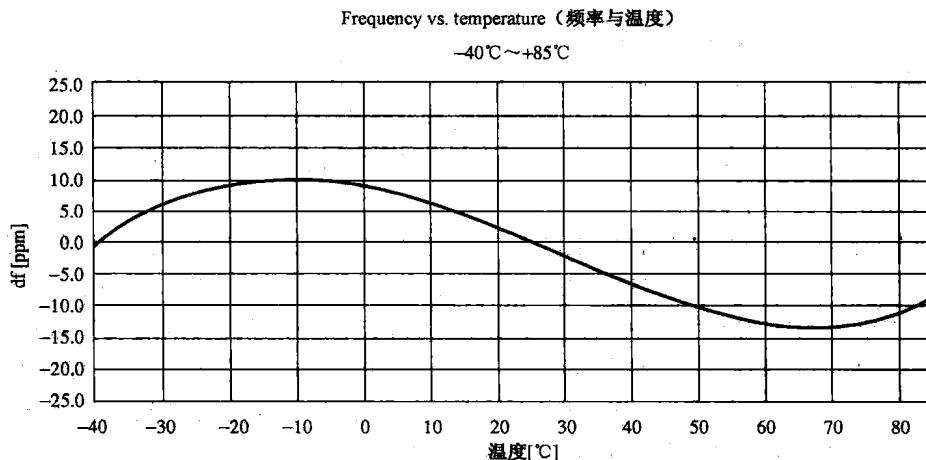

| 【案例 6-5】 高温流量测试丢包问题                          | 148        |

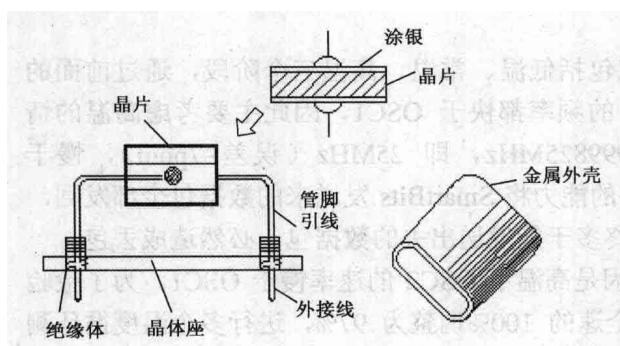

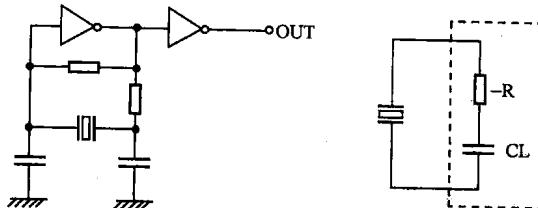

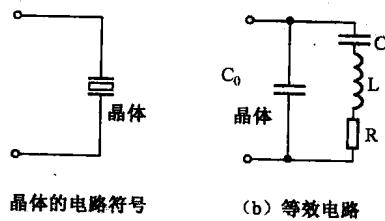

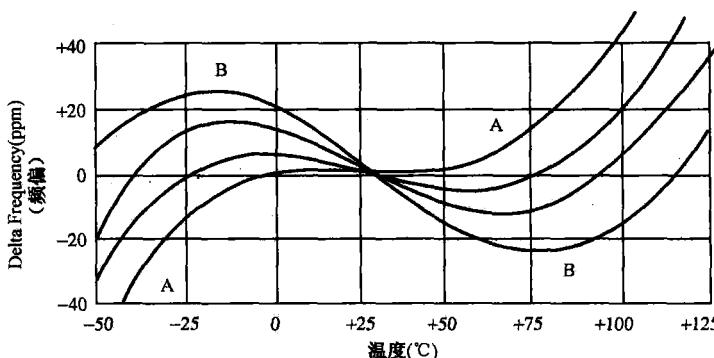

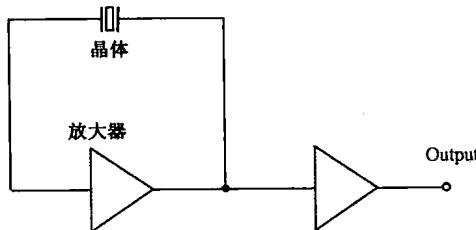

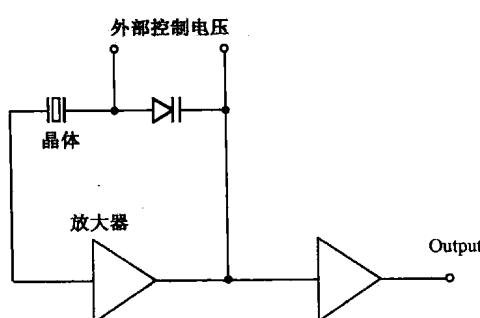

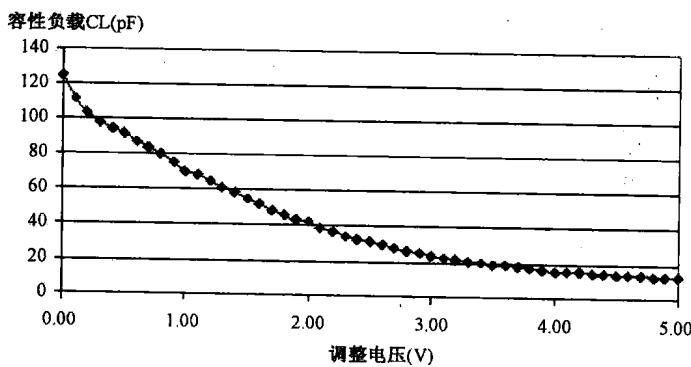

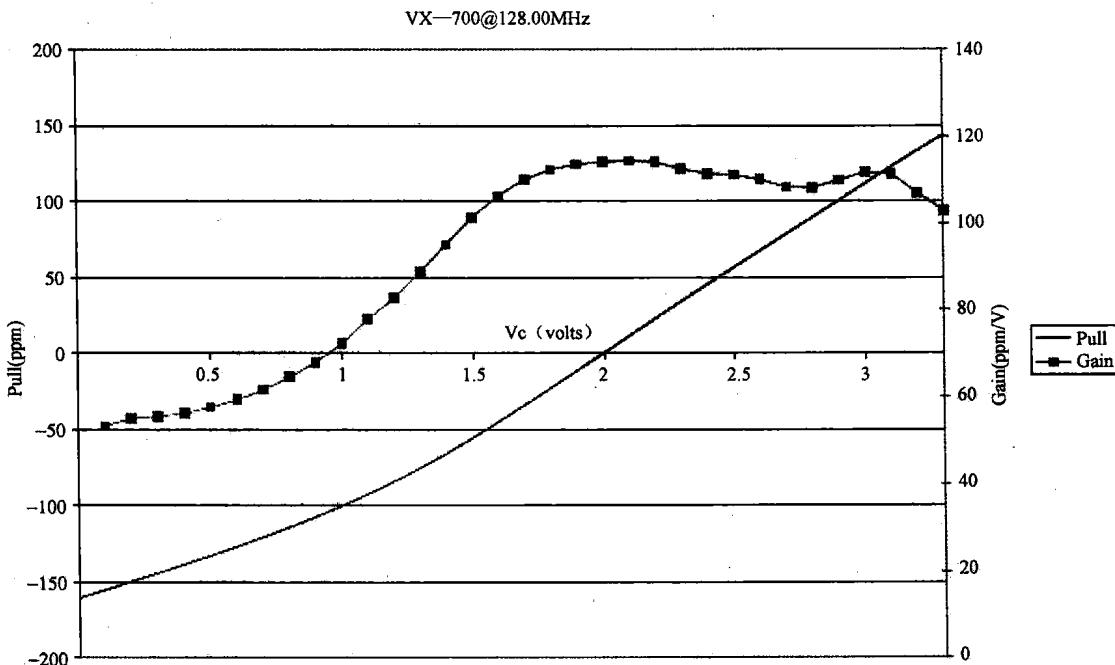

| 6.2.2 晶体、晶振介绍及其应用要点                          | 150        |

| 【案例 6-6】 利用首个时钟沿启动组合逻辑导致 CPU 工作不稳定           | 153        |

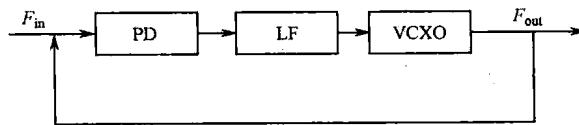

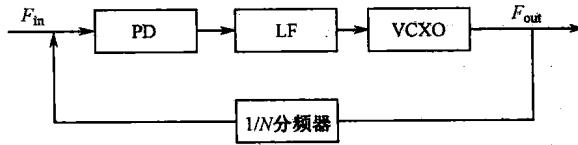

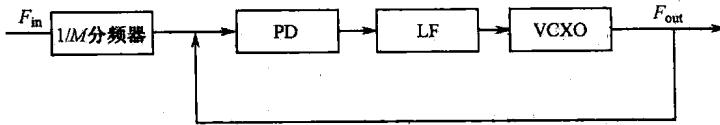

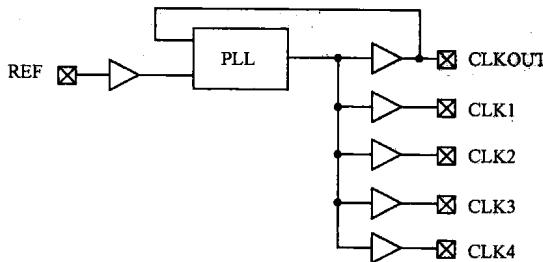

| 6.2.3 锁相环及其应用                                | 157        |

| 【案例 6-7】 两级锁相环的应用导致 MPC8280 的 PCI 时钟失锁       | 162        |

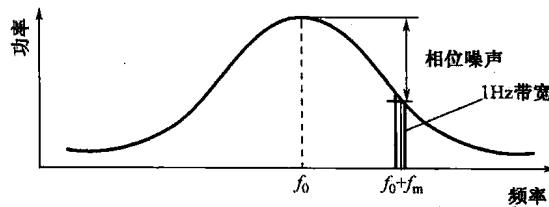

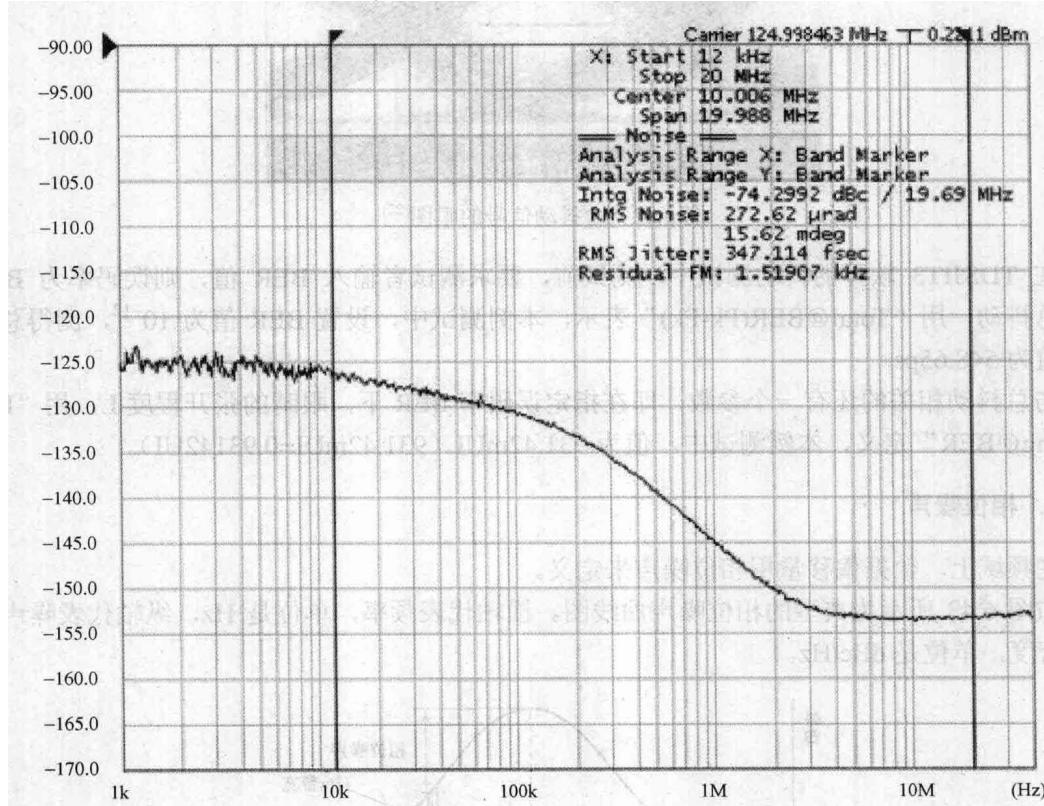

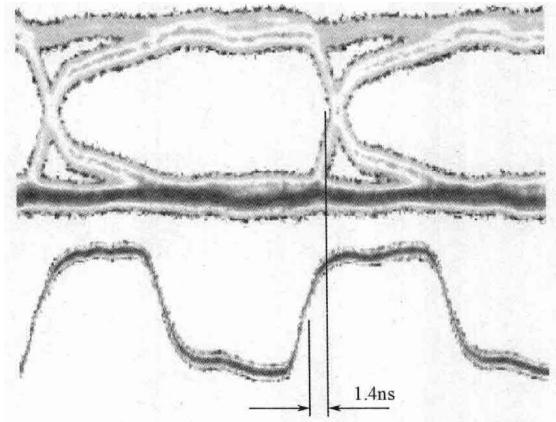

| 6.2.4 时钟抖动与相位噪声                              | 164        |

| <b>第 7 章 高速电路中的存储器应用与设计</b>                  | <b>172</b> |

| 7.1 与存储器相关的经典案例                              | 172        |

| 【案例 7-1】 时序裕量不足导致存储器测试出错                     | 172        |

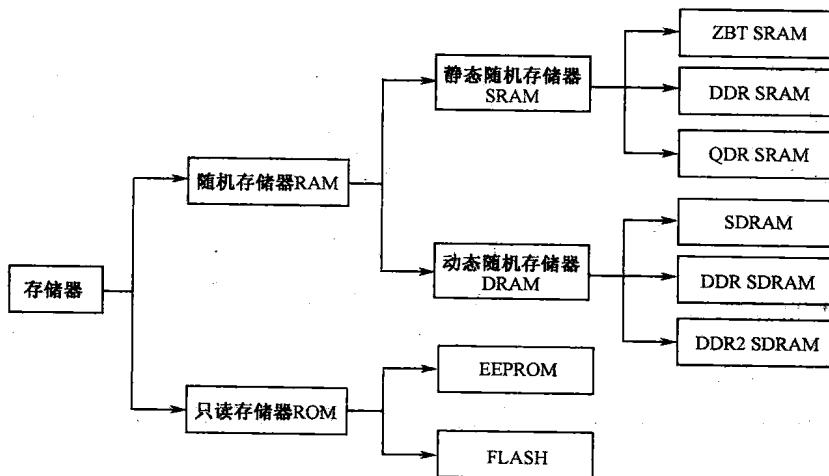

| 7.2 常用存储器介绍及其应用要点                            | 174        |

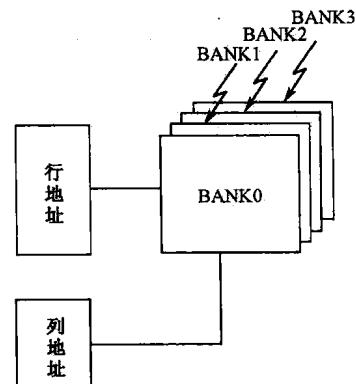

| 7.2.1 存储器概述                                  | 174        |

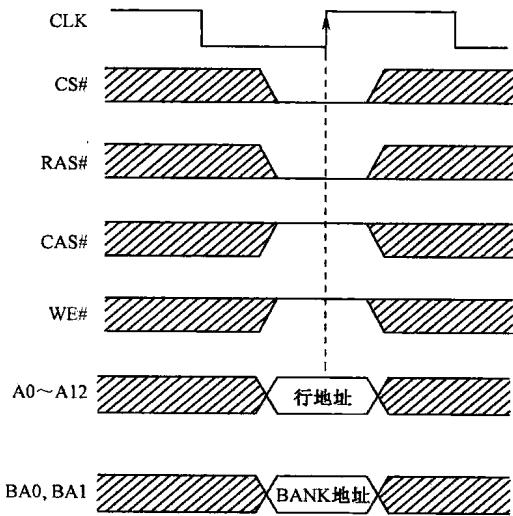

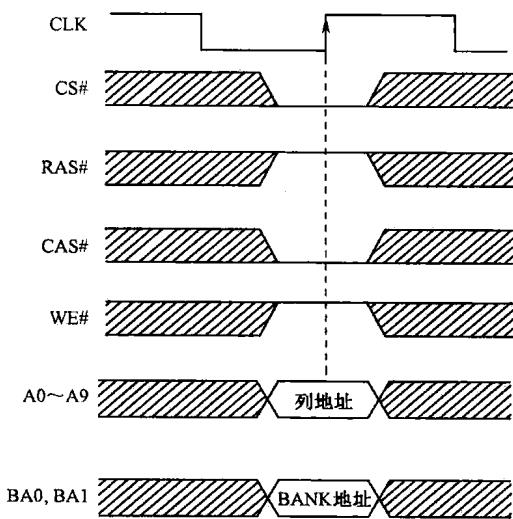

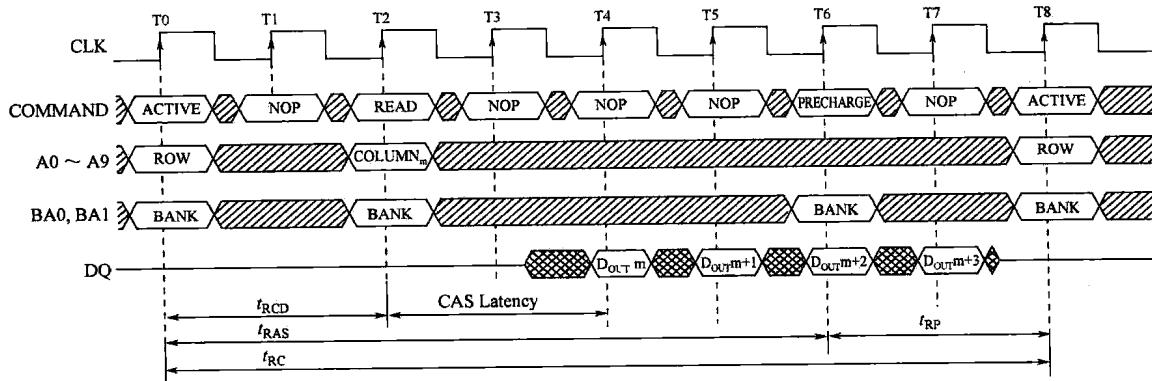

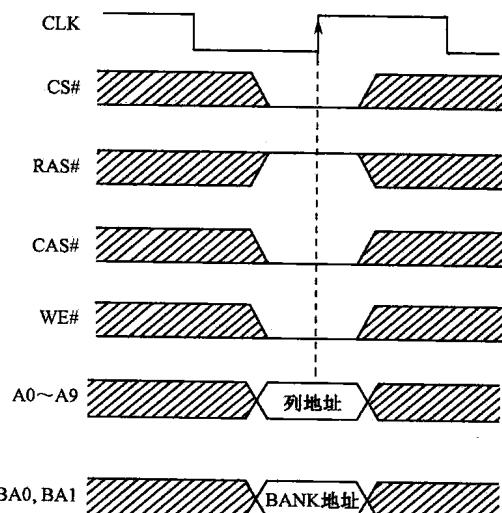

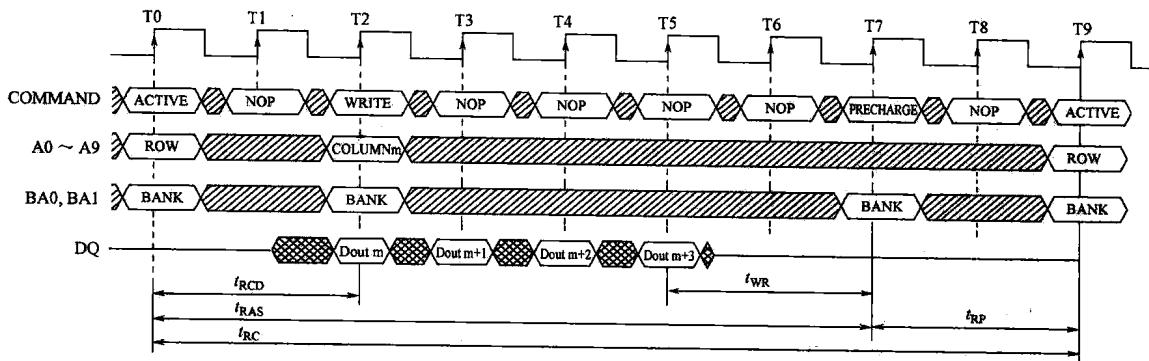

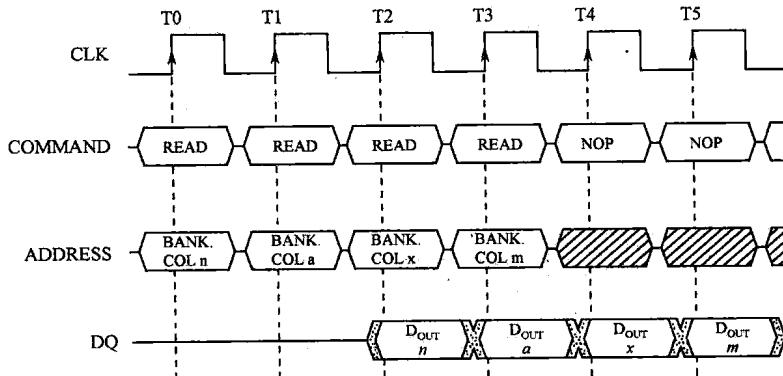

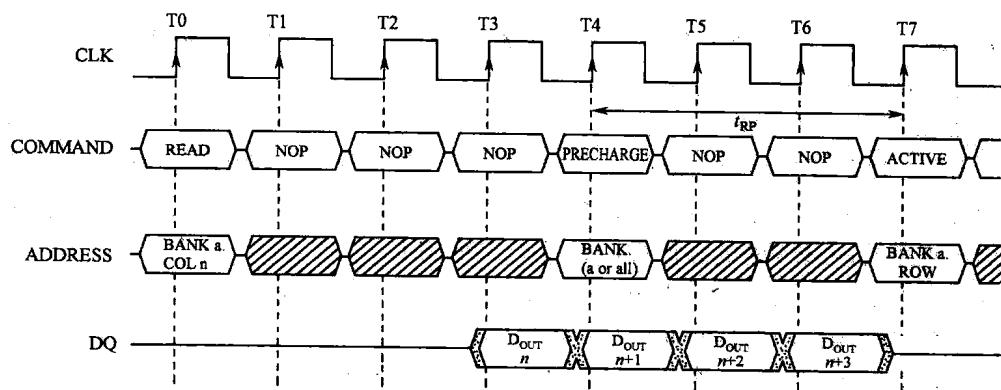

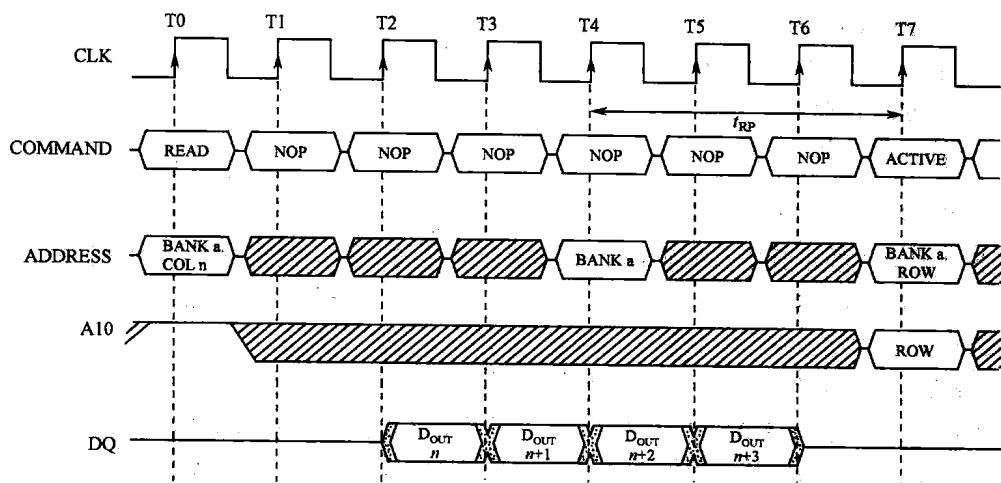

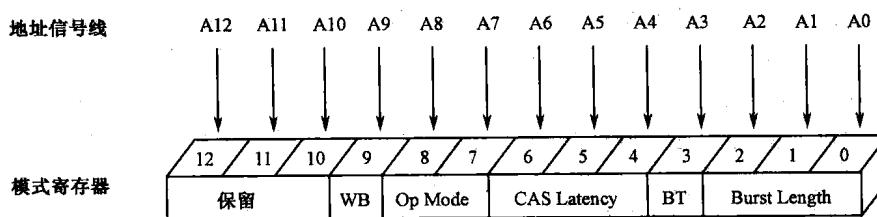

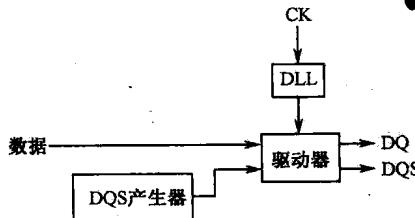

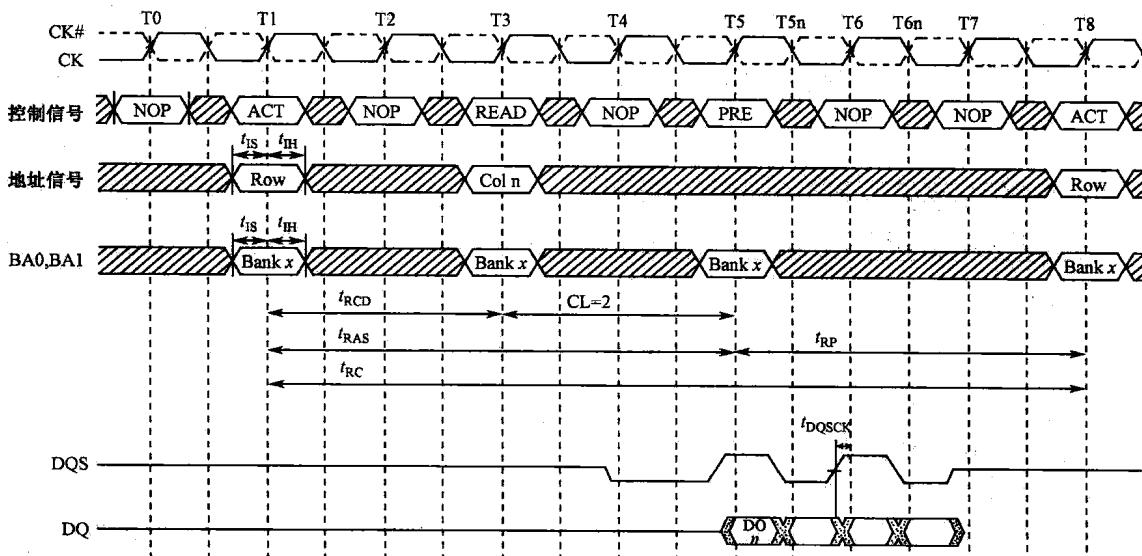

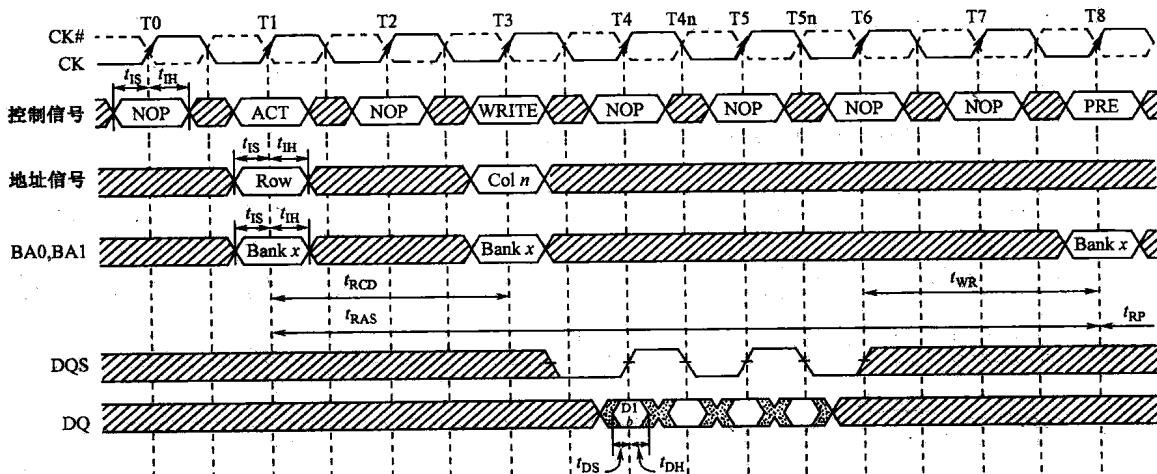

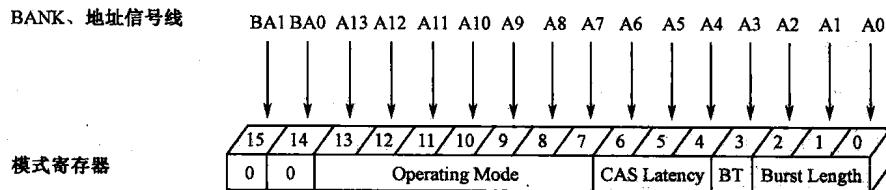

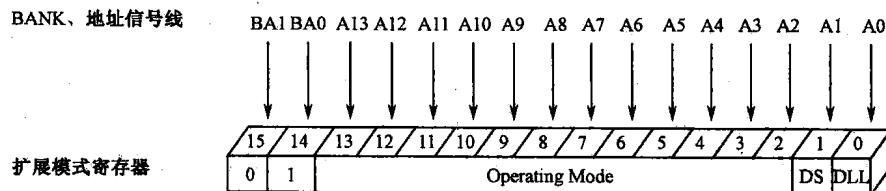

| 7.2.2 SDRAM 介绍及其应用要点                         | 176        |

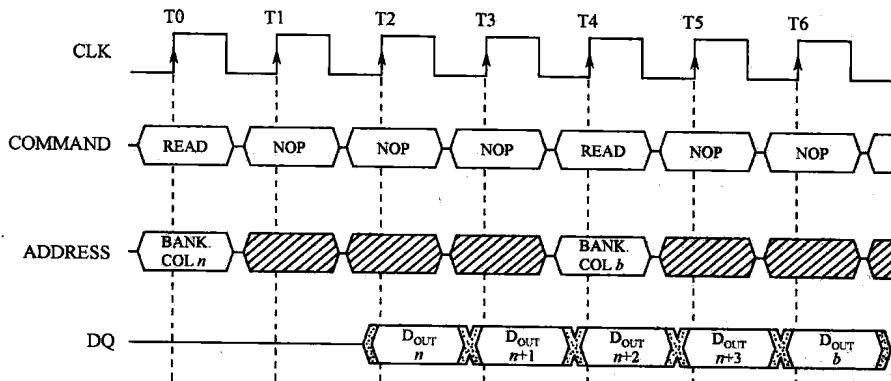

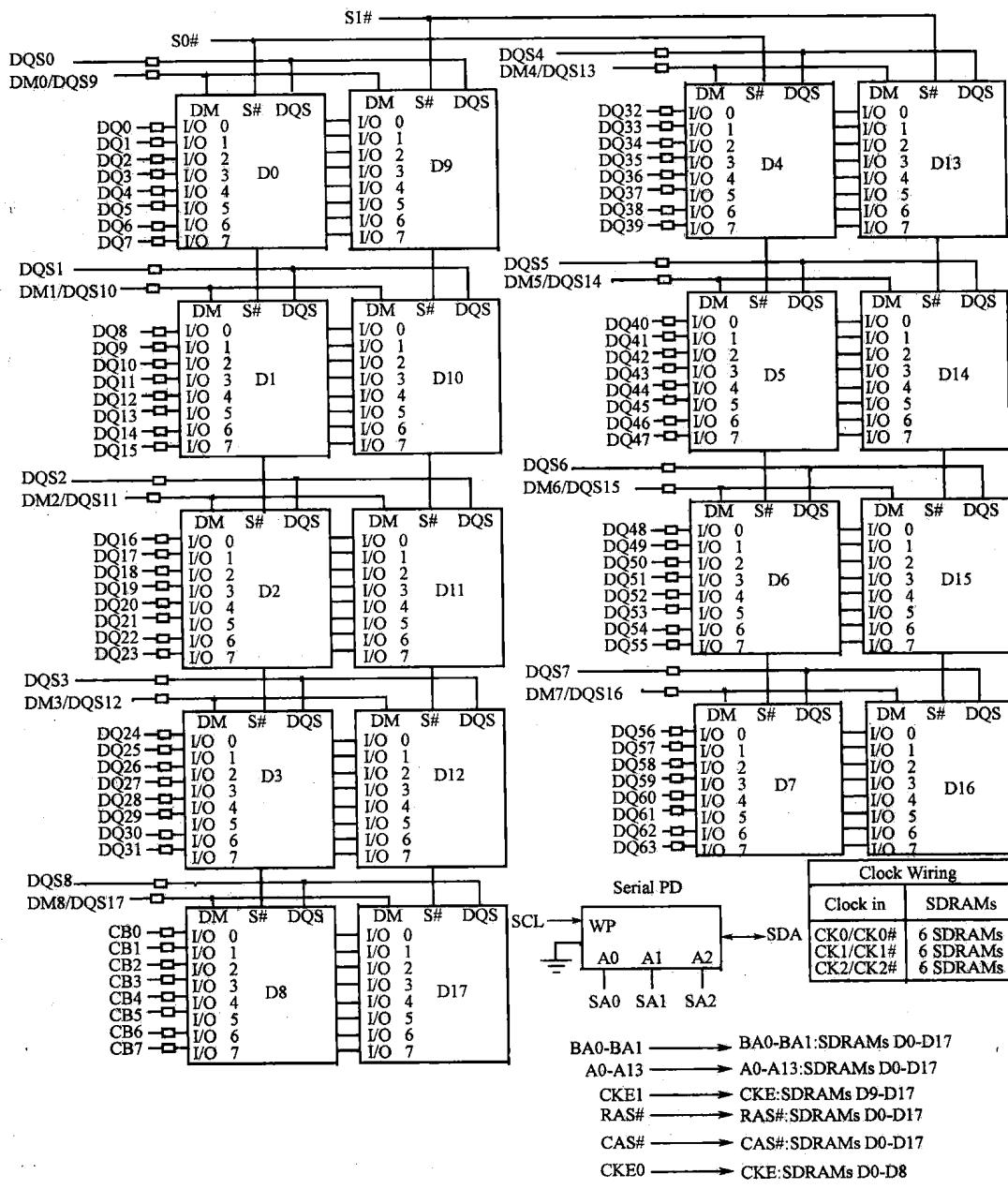

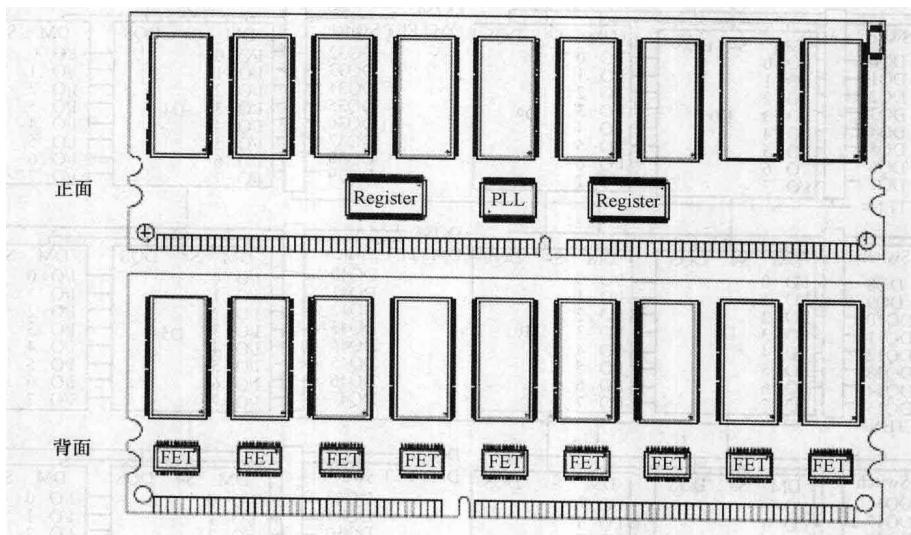

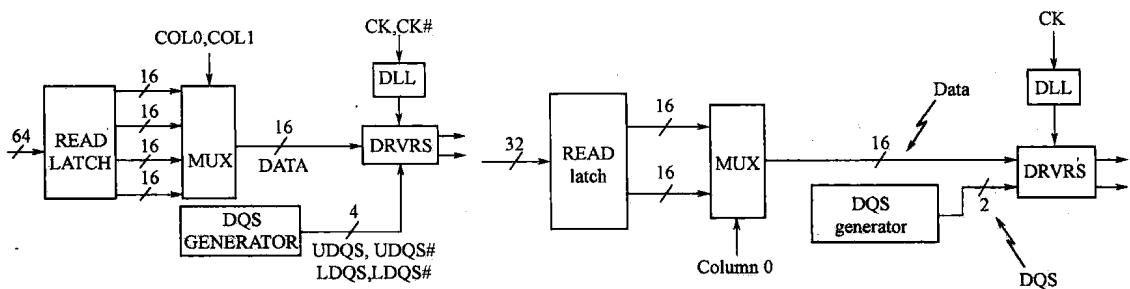

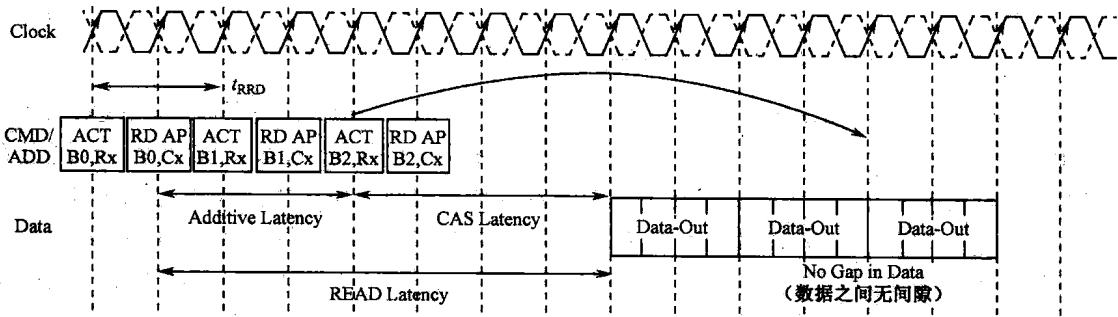

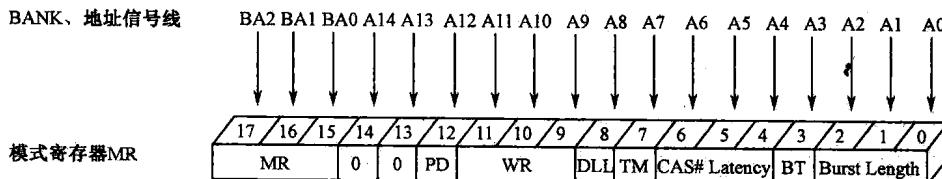

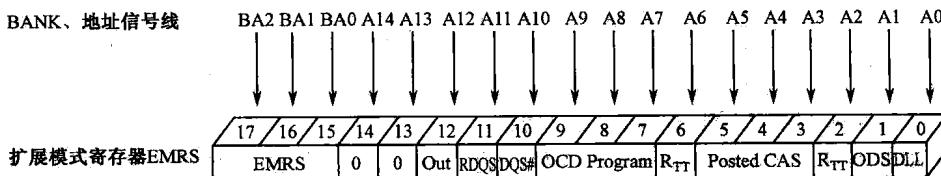

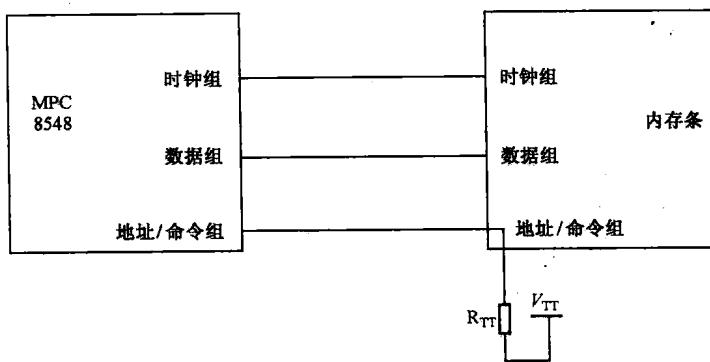

| 7.2.3 DDR SDRAM 介绍及其应用要点                     | 188        |

| 【案例 7-2】 DLL 缺陷造成 DDR SDRAM 时序出错             | 192        |

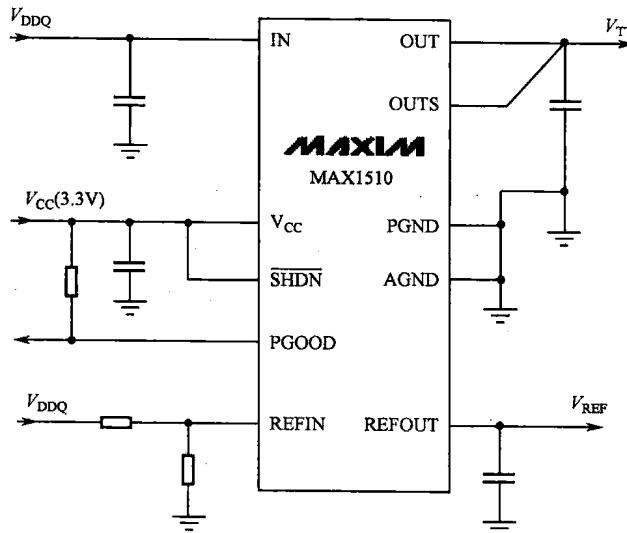

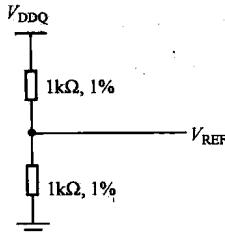

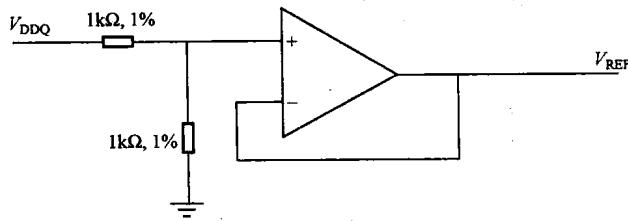

| 【案例 7-3】 $V_{REF}$ 不稳定造成存储器读写操作出错            | 198        |

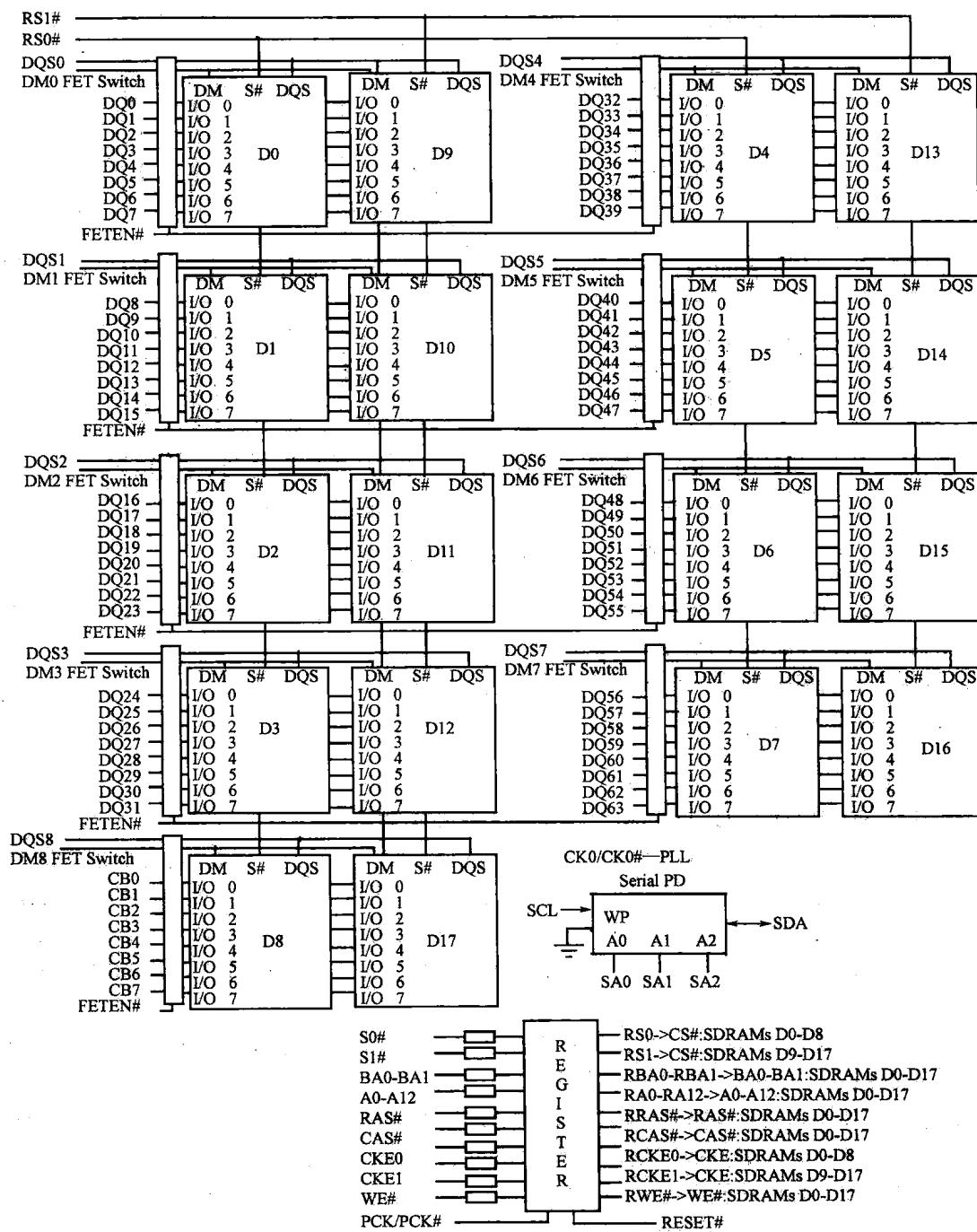

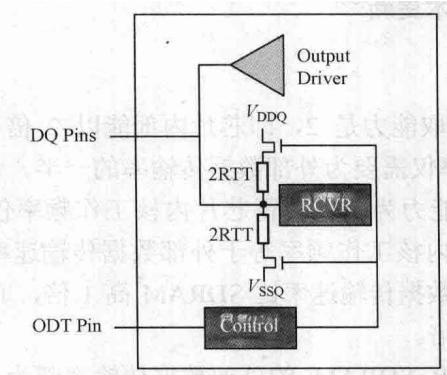

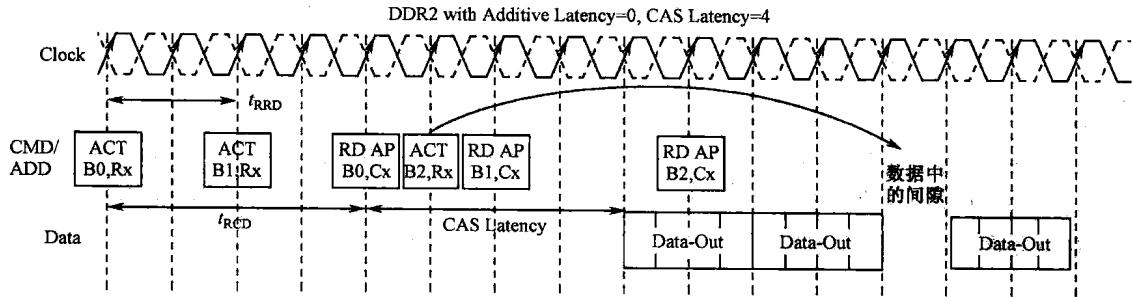

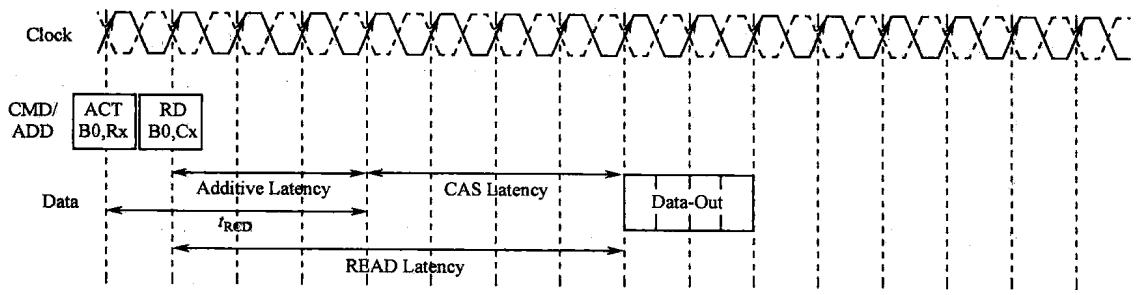

| 7.2.4 DDR2 SDRAM 介绍及其应用要点                    | 203        |

| 【案例 7-4】 CPU 存储系统不识别 8 位内存条的问题               | 211        |

| 7.2.5 SRAM 介绍及其应用要点                          | 212        |

| 【案例 7-5】 片选处理不当导致 SRAM 数据丢失                  | 214        |

| 7.2.6 FLASH 与 EEPROM 介绍                      | 227        |

| 【案例 7-6】 热插拔导致单板 FLASH 损坏                    | 227        |

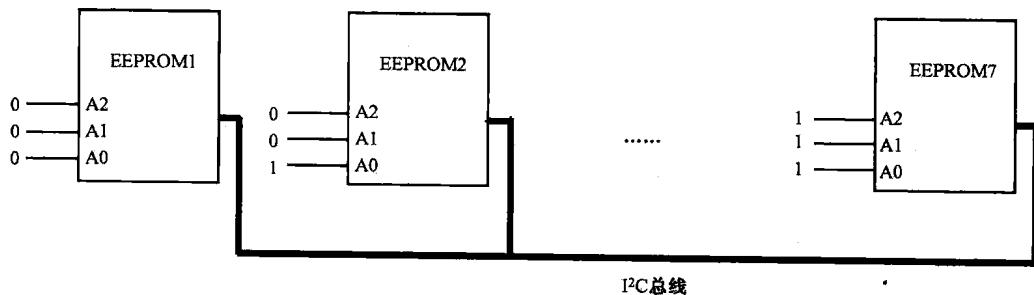

| 【案例 7-7】 读取百兆光模块信息出错                         | 231        |

| <b>第 8 章 高速电路中的 PCB 及其完整性设计</b>              | <b>232</b> |

| 8.1 与 PCB 及完整性设计相关的经典案例                      | 232        |

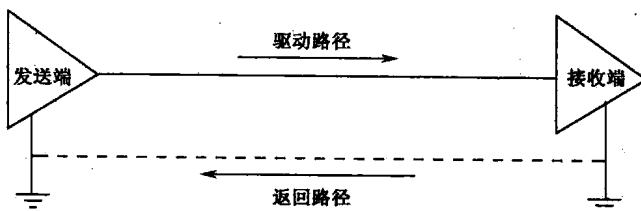

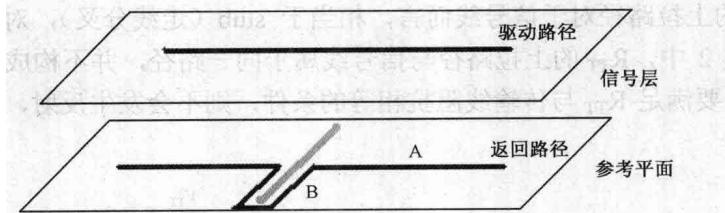

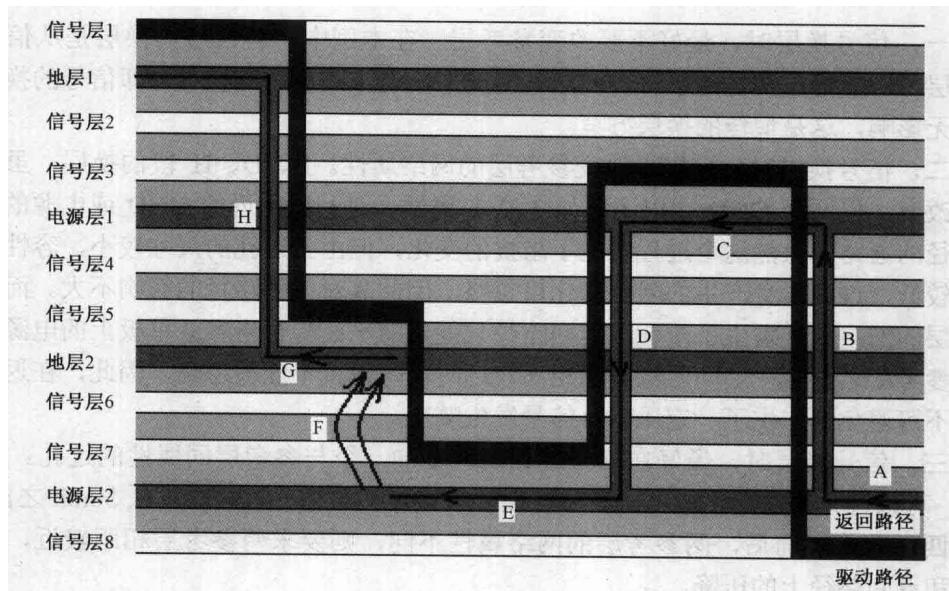

| 【案例 8-1】 回流路径缺陷对高速信号质量的影响                    | 232        |

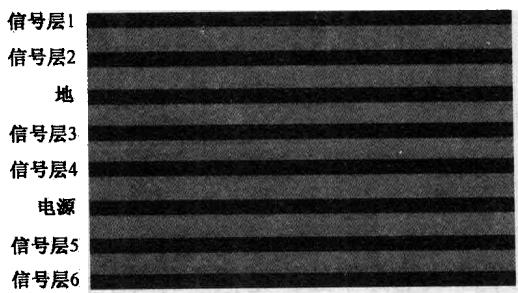

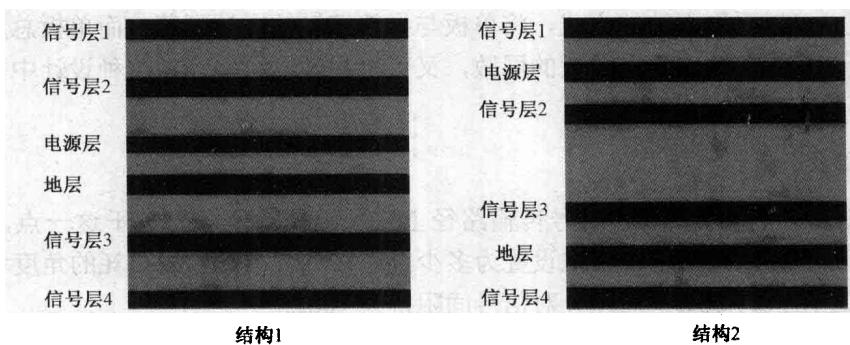

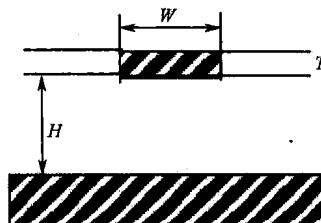

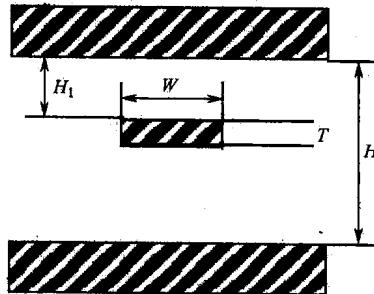

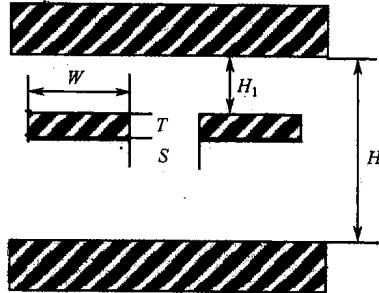

| 8.2 PCB 层叠结构与阻抗计算                            | 234        |

| 8.2.1 Core 和 PP                              | 234        |

| 8.2.2 PCB 的层叠结构和阻抗设计                         | 234        |

| 8.3 高速电路 PCB 设计要点                            | 241        |

| 8.3.1 PCB 设计与信号完整性                           | 241        |

| 【案例 8-2】 传输线的判断                              | 241        |

| 【案例 8-3】 反射的计算                               | 242        |

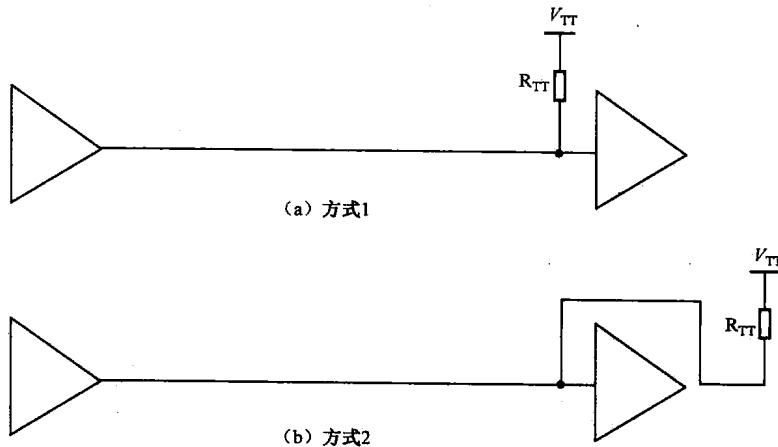

| 【案例 8-4】 DDR SDRAM 设计时，终端电阻 RTT 布放位置的选择      | 244        |

| 【案例 8-5】 大驱动电流信号对高速数据信号的串扰                   | 250        |

| 【案例 8-6】 高速接口器件批次更换造成辐射超标                    | 252        |

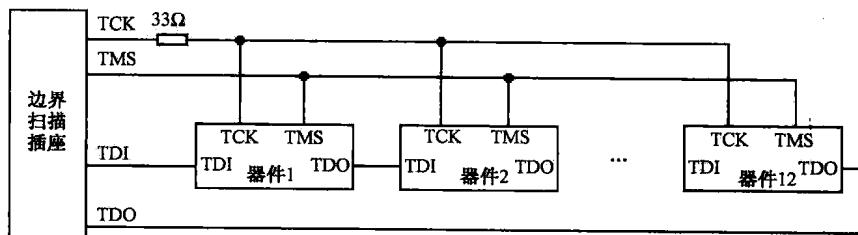

| 【案例 8-7】 TCK 信号出现回沟导致无法通过 JTAG 接口对 CPLD 进行加载 | 256        |

|                                           |            |

|-------------------------------------------|------------|

| 8.3.2 PCB 设计与电源完整性 .....                  | 257        |

| 8.3.3 PCB 设计中的 EMC .....                  | 260        |

| 【案例 8-8】 网口指示灯信号线引发的辐射问题 .....            | 264        |

| 【案例 8-9】 接口芯片与时钟驱动器共用电源，导致辐射超标 .....      | 266        |

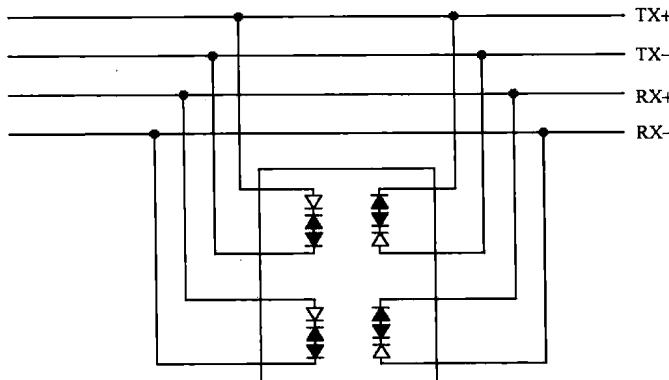

| 8.3.4 PCB 设计中的 ESD 防护 .....               | 267        |

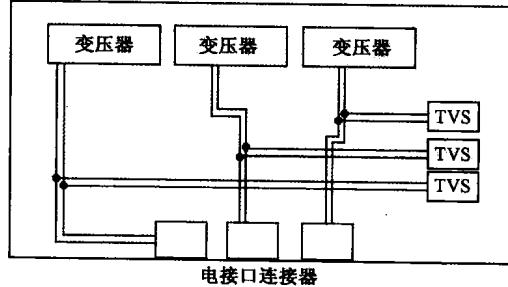

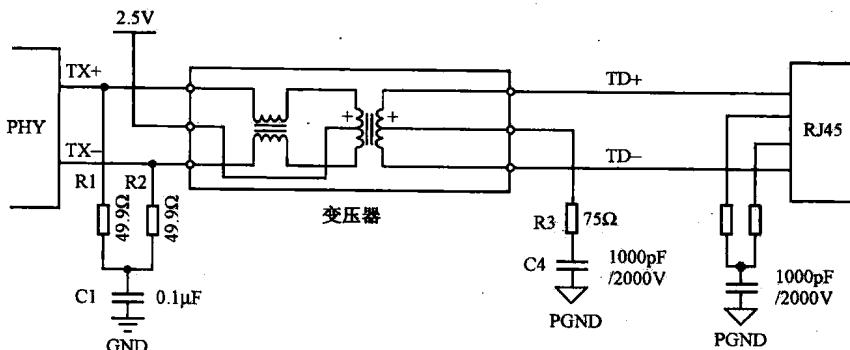

| 【案例 8-10】 TVS 管布放位置不合理导致静电放电测试失败 .....    | 268        |

| 【案例 8-11】 GND 和 HV_GND 混用导致电源控制电路失效 ..... | 270        |

| 8.3.5 PCB 设计与结构、易用性 .....                 | 272        |

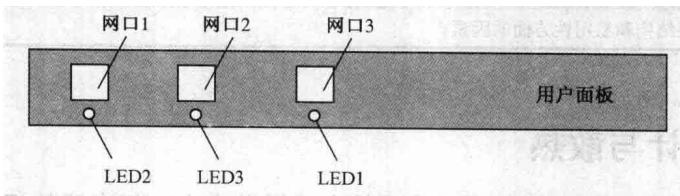

| 【案例 8-12】 网口指示灯排列顺序出错 .....               | 273        |

| 【案例 8-13】 网口连接器堆叠方式与易插拔特性 .....           | 273        |

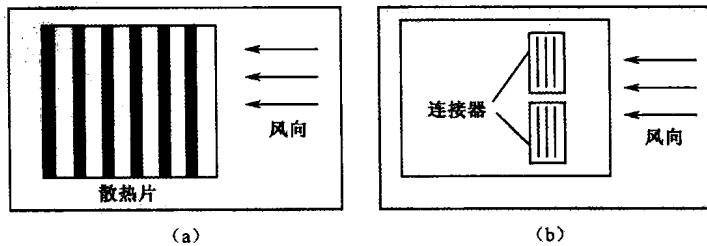

| 8.3.6 PCB 设计与散热 .....                     | 274        |

| 8.3.7 PCB 设计与可测试性 .....                   | 275        |

| <b>参考文献 .....</b>                         | <b>279</b> |

# 第1章 概述

## 1.1 低速设计和高速设计的例子

本节通过一个简单的例子，探讨高速电路设计相对于低速电路设计需要考虑哪些不同的问题。希望读者通过本例，对高速电路设计建立一个表象的认识。至于高速电路设计中各方面的设计要点，将在后续章节展开详细的讨论。

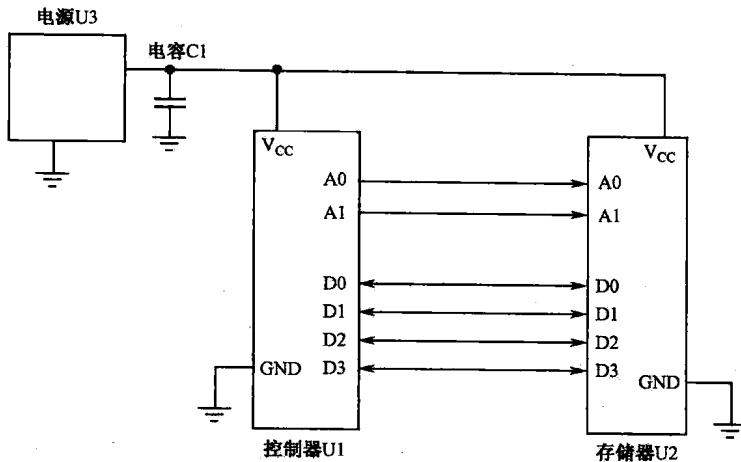

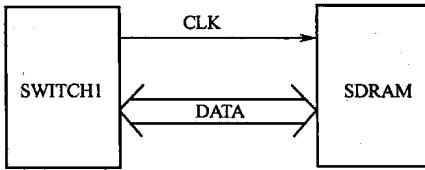

### 【案例 1-1】 简化的存储电路模块

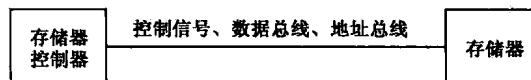

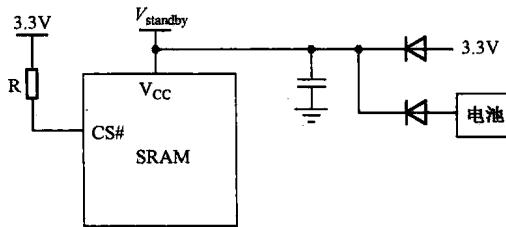

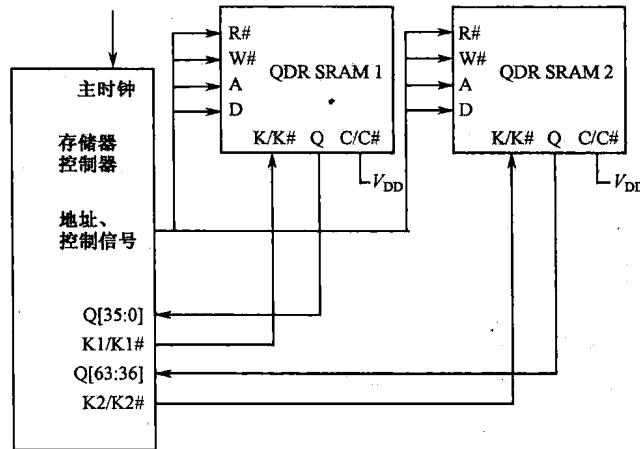

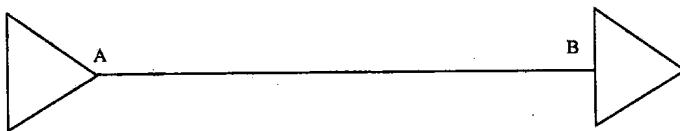

图 1.1 是一个经简化后典型的存储模块原理图。对于同样的简化原理图，根据以下两种不同的客户需求，需要设计不同的存储系统，一种是低速系统，一种是高速系统。

图 1.1 一个简化的存储电路模块

#### 1.1.1 低速设计

第一个客户需求是，设计一套机床台面振动监测系统，要求每 20ms (ms: 毫秒) 检测一次振动信息，然后把数据存储到存储器内，每分钟把存储器内存储的 3000 个数据读取出来，并做一定的运算处理（该算法的实现方式是，读取一个数据即处理一次，数据处理完成即丢弃），得到一个体现一分钟内振动量的值，并在显示器上显示，数据读取和处理的过程不超过 1s (s: 秒)，在此期间，可以暂停数据采样。

首先进行需求分析。这是一套采样速率为 0.02 秒/次的采样系统，每 0.02s 对振动信息采样一次并存储到存储器里，则每 60s 需要对 3000 个数据进行运算处理并通过串口，将运算结果传出去。振动传感器的选型及其放大电路的设计不在本例中讨论，本例主要研究该监测系统的存储部分。另外，假定传感器输出电信号的采样值用 8 位二进制，即一个字节表示。

从成本以及功能考虑，可以选择由单片机及小容量存储器组建存储系统。

U1 选择某款 51 系列的单片机，主频为 12MHz (MHz: 兆赫兹)，外部总线的最高运行速率可达 1MHz，U2 选择为能和该单片机直接接口的小容量 RAM (随机存储器)。在本例中，采样速率的要求是 50Hz (每 0.02s 采样一次)，则存储器写入的速度可设定为 0.0025 秒/位 (0.02 秒/8 位)，假定单片机对数据的处理时间相对于读取时间可以忽略，则存储器读取速度可设定为 42 微秒/位 (1 秒/3000/8 位)。

主要芯片选型完成后，进行详细设计。

该电路耗电不多，因此电源 U3 选用 LDO (低压差线性稳压器)，电容 C1 是电源的去耦电容，根据 U3 器件资料的要求，选取为 10μF (μF: 微法)。本设计所要求的数据传输速率较慢，是一个典型的低速电路，可以采用集总式系统的思维来分析。在设计中需要考虑以下要点：

(1) CPU 和存储器选型。选择 51 系列的单片机和小容量的 RAM，这在需求分析阶段已经完成。

(2) 总功耗。即 U1、U2 全速运行时，整个电路板的最大功耗，要求电源 U3 必须能提供该最大功率，且还留有 20% 的裕量。例如，U1 的最大功耗是 140mW (mW: 毫瓦)，U2 的最大功耗是 60mW，则要求 U3 至少能提供 240mW 的功率。如果 U1、U2 的工作电源电压  $V_{CC}$  都是 5V，则要求 U3 至少能提供电流 50mA (mA: 毫安)。

(3) 电源 U3 选型。根据第 4 章的内容，可以选择低成本且应用简单的 LDO 类型的电源器件，如 7805。

(4) 电容 C1 选型。根据第 4 章的内容，选择 10μF 钽电容。

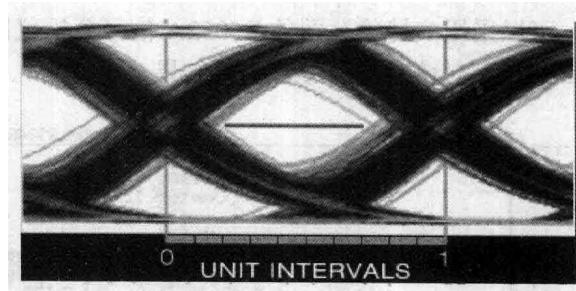

## 1.1.2 高速设计

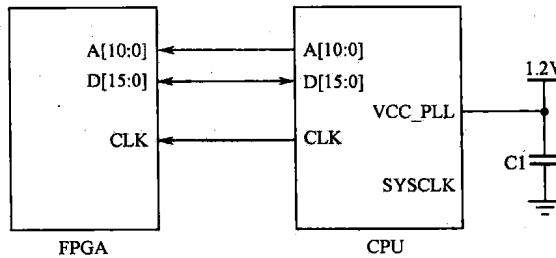

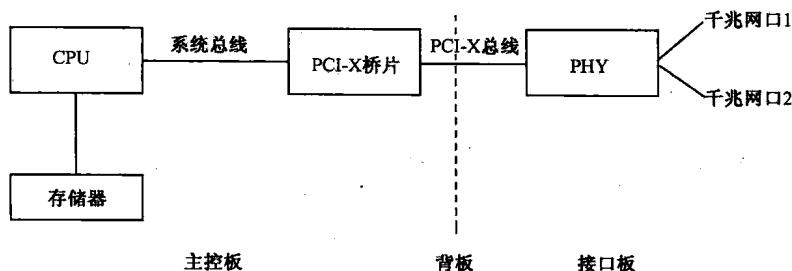

第二个客户的需求是，设计一套应用在以太网交换机的主控板，该交换机需要支持 12 个 GE (GE: 千兆以太网) 口，且支持三层交换。本例仍仅讨论存储部分的设计。

简化后的原理图仍然采用图 1.1，不过在本例中，我们将采用不同的芯片来组建高速电路。这是一个典型的高速电路，需要采用分布式系统的思维来分析。

(1) CPU 选型。在三层交换机中，主控板 CPU 需要支持全系统的控制链路，还需要支持以太网的很多特性。经过仔细的性能分析后，U1 选用内部工作频率达 1.5GHz (GHz: 吉赫兹， $1\text{GHz} = 10^3\text{MHz}$ ) 的 Freescale 公司的 PowerPC: MPC8547。

(2) 存储器选型。根据性能需要，U2 选用 Micron 公司的数据速率达 667Mbps (Mbps: 兆比特位每秒) 的 DDR2 SDRAM DIMM 条，总容量为 1GB (GB: 吉字节)。本书第 7 章将详细讨论 DDR2 SDRAM 存储器的选型与应用。

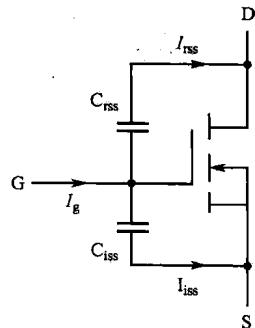

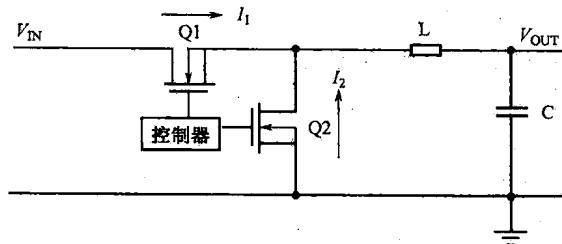

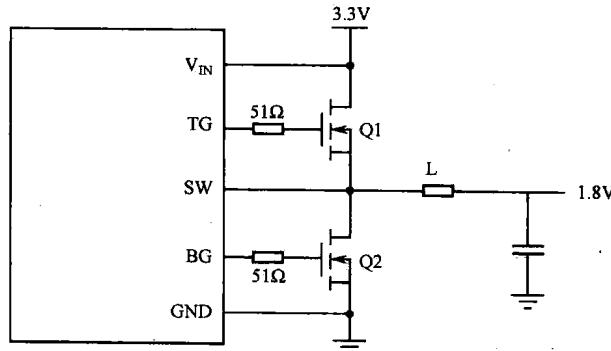

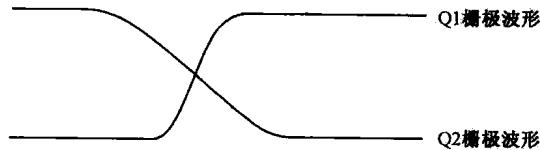

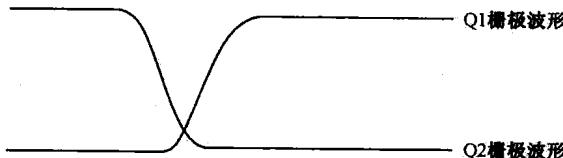

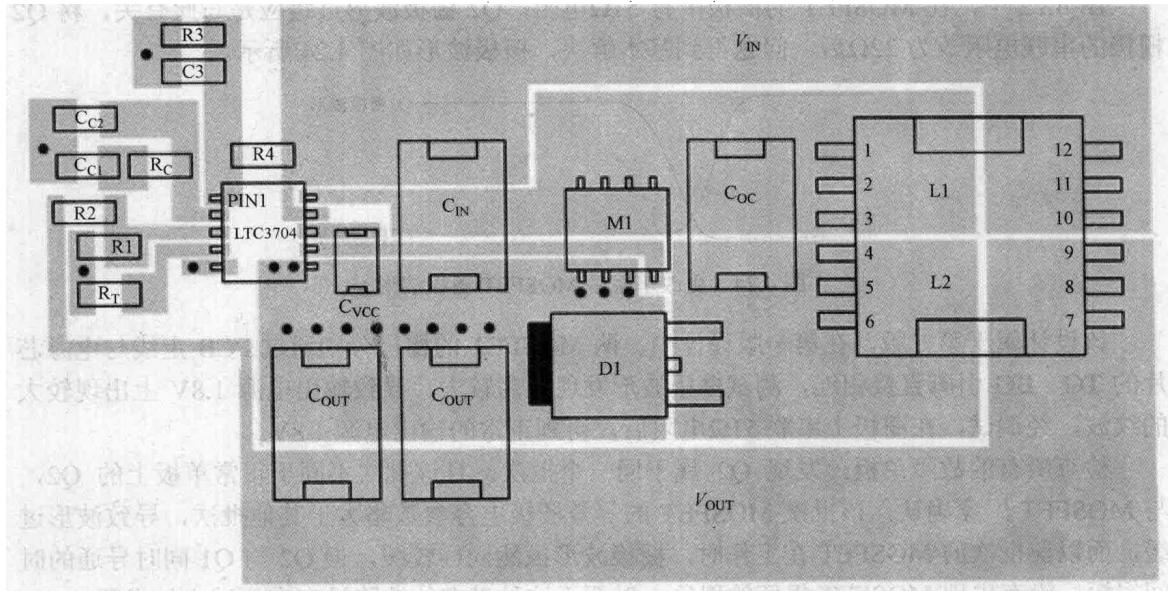

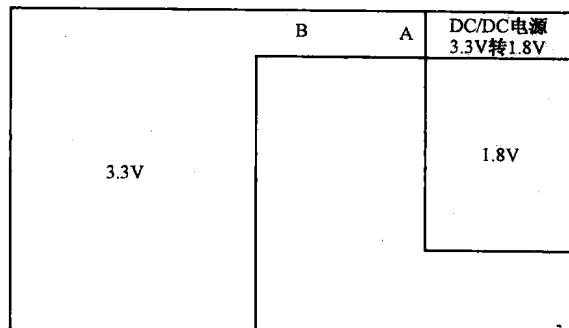

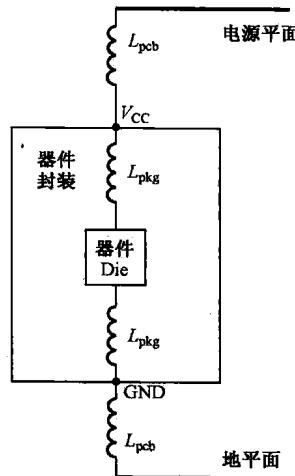

(3) 电源选型。为简化描述，此处仅考虑 MPC8547 和 DDR2 SDRAM DIMM 条之间共同的电源 1.8V，并假设图 1.1 中  $V_{CC}$  为 1.8V。U3 需选择能输出 1.8V 的 DC/DC 电源芯片，具体选型考虑的因素将在本书第 4 章中介绍。DC/DC 电源芯片的工作需要配合电感、MOSFET (金属半导体场效应管)、电容等器件。对电感、电容等器件的选型，可参考本书第 2 章的内容，对 MOSFET 器件的选型，可参考本书第 4 章的内容。

(4) 电容 C1 选型。C1 可选择为 220μF 的钽电容，具体选型的依据将在本书第 4 章中介绍；根据 U1 和 U2 的工作电压，C1 的额定电压可以选择为 6.3V；根据 PCB (PCB: 印

制电路板) 的空间要求, 电容的尺寸可选择为 2412 (将在本书第 2 章中介绍); 为保证 U1 和 U2 的稳定工作, 要求电容精度达到 10%; 由于运行速度高, 该电容还需要有较小的 ESR (等效串阻) 以实现快速响应。对电容的选型, 将在第 2 章中详细介绍。

(5) 除 C1 以外, 还需要给  $V_{CC}$  提供其他电容, 以滤除电源电路上的干扰。在本书第 4 章和第 8 章中将介绍, 当器件高速运行时, 在电源  $V_{CC}$  上将产生较大的高频噪声, 为了保证高速器件获得干净的电源, 需要在 U1 和 U2 的每个  $V_{CC}$  电源引脚处, 就近放置一个容值为  $0.1\mu F$  或者  $1\mu F$  的陶瓷电容; 根据 PCB 上可使用的面积, 建议选择小尺寸封装的电容, 如 0402 尺寸; 在功耗较大的设计中, 还应考虑温度稳定性, 需要选用 X7R 的电容类型; 根据器件工作电压, 电容的额定电压可选择为 10V。这一部分的选型, 涉及本书第 2、4 章的相关内容。

(6) 逻辑器件选型。在 U1 和 U2 之间, 如果由于速率或者工作电压不同而无法直接接口, 则还需要用到逻辑器件以实现桥接, 可参考本书第 3 章的相关内容进行逻辑器件的选型和应用。

(7) 时序分析。高速电路中, 信号在 PCB 上的走线长度对器件的时序要求至关重要, 本书第 5 章将详细介绍时序分析和设计的方法。

(8) 复位和时钟电路设计。MPC8547 有多种复位要求, 如上电复位、硬件复位、软件复位等, 同时还要求提供多种时钟 (如内核工作时钟, 接口时钟等), 关于复位和时钟电路的详细设计要求, 可参考本书第 6 章的内容。

(9) 原理图和 PCB 的设计。经过前面的步骤, 在完成对各种器件的选型后, 对原理图的绘制, 可参考本书第 1 章的内容, 而对 PCB 的设计, 可参考本书第 8 章的内容。

(10) 防护和 EMC (电磁兼容性) 设计。对高速接口, 还需要参考本书第 8 章的内容, 以进行防护和 EMC 设计。

(11) 调试。设计完成后, 需要验证电路的功能。该设计属于高速设计, 因此, 还需要对单板上的电源、高速信号等进行相关测试, 相关内容将在第 4、7、8 章介绍。

由此可见, 相对低速电路设计, 高速电路设计要求设计者考虑的因素更多, 本书的后续章节, 将一一探讨这些内容。

## 1.2 如何区分高速和低速

高速设计区别于低速设计, 简单来说, 就是分布式系统思维和集总式系统思维的区别。

那么, 多高的信号速度才算高速? 在讨论这个问题之前, 需要注意避免进入以下两个误区:

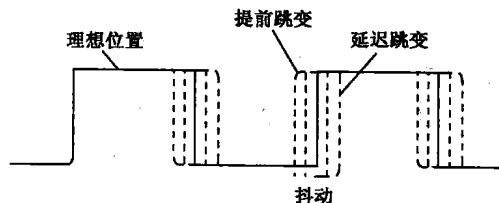

**误区 1** 信号周期频率  $F_{clock}$  高的才属于高速设计。事实上, 设计中需要考虑的最高频率往往取决于信号的有效频率 (或称转折频率)  $F_{knee}$ 。<sup>[1]</sup>

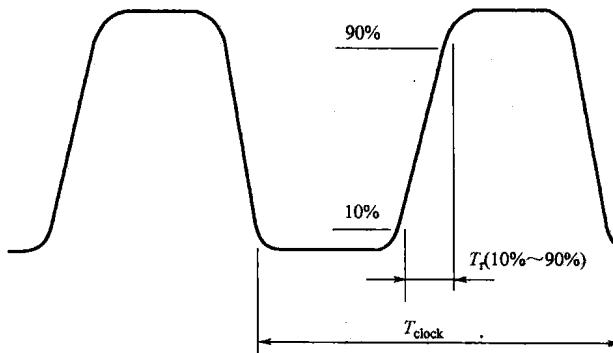

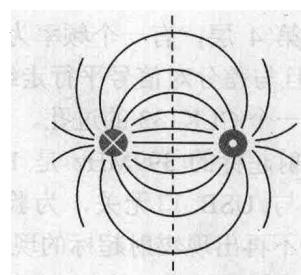

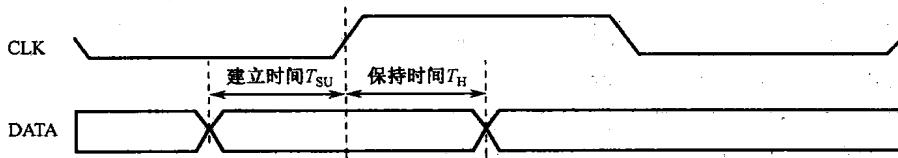

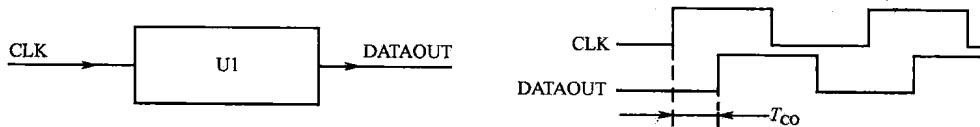

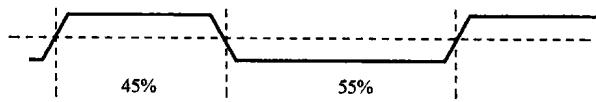

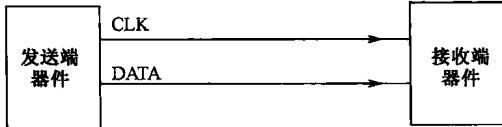

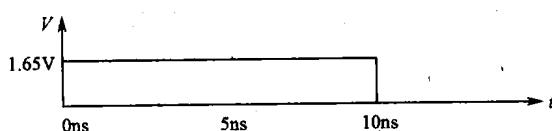

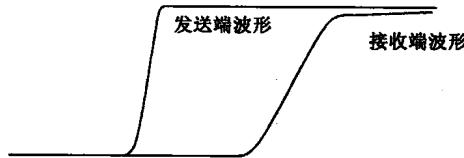

如图 1.2 所示,  $T_{clock}$  是信号的时钟周期,  $T_{r(10\% \sim 90\%)}$  是信号的 10%~90% 上升时间, 则信号的周期频率与有效频率分别定义为:

$$F_{clock} = 1/T_{clock} \quad (1.1)$$

$$F_{knee} = 0.5/T_{r(10\% \sim 90\%)}^{[1]} \quad (1.2)$$

图 1.2 信号的时钟周期和 10%~90% 上升时间

由数字信号处理的知识可知，现实世界中的任何信号都是由多个频率分量的正弦波叠加而成的。以方波为例，周期频率为  $F$  的理想方波，由频率为  $F$  的正弦波及其奇数次谐波（频率分别为  $3F$ 、 $5F$ 、 $7F$  等）组成，定义各正弦波分量的幅值为  $V_N$ ，其计算公式为：

$$V_N = 2 / (3.14 \times N) \quad (1.3)$$

根据式 (1.3)，一次谐波分量的幅值  $V_1=0.64V$ ，三次谐波分量的幅值  $V_3=0.21V$ ，五次谐波分量的幅值  $V_5=0.13V$ 。即随着频率的升高，各级谐波分量的幅值与频率成反比。

现实中的信号，随着频率的升高，其各级谐波分量的幅值比理想方波中相同频率正弦波分量的幅值下降得更快，直到某级谐波分量，其幅值下降到理想方波中对应分量的 70%（即功率下降到 50%），定义该谐波分量的频率为信号的有效频率<sup>[57]</sup>。对现实中的多数信号而言，有效频率可由式 (1.2) 计算。

### 误区 2 电容、电感是理想的器件。

在低速领域，电容、电感的工作频段比较低，可以认为它们都是理想的器件。但在高速领域，电路板上的电容、电感等已经不能被简单地视为纯粹的电容、电感。例如，当电路的两端用一个电容  $C$  相连时，在低速电路中，这两端被视为断路，而在高速电路中，假定其工作频率为  $F$ ，则电容  $C$  表现出的电抗值为  $1/(2\pi F \times C)$ ，在工作频率很高的情况下，该电容  $C$  的电抗值变得很小，表现为短路。同理，在低速电路中表现为短路的电感，在高速电路中将表现为断路。本书第 2 章将详细介绍在何种频率点上，电容和电感将发生这种属性的变化。

在认清了以上两个误区后，我们再重新回到如何区分低速信号与高速信号的问题。

这里讲的低速信号为传输路径上各点的电平大致相同的信号，高速信号为传输路径上各点电平存在较大差异的信号。

对低速信号而言，由于传输路径上各点电平近似相同，因此，可采用集总式的思维来看待传输路径，即传输路径上各点的状态相同，在分析时，可被集中成一点；对高速信号而言，传输路径上各点的电平不同，需采用分布式的思维来看待传输路径，即不能将传输路径集中成一点来看待，而应视为多个状态不同的点。

由此可知，高速与低速的区分，不仅取决于信号频率，还取决于信号传输路径的长度，仅仅依据信号频率，并不能做出信号属于高速还是低速的结论。

一般而言，在信号传输路径的长度（即信号线的长度）小于信号有效波长的  $1/6$  时，可认为在该传输路径上，各点的电平状态近似相同。

信号波长与信号频率的关系如下：

$$\lambda = c/F \quad (1.4)$$

式中  $\lambda$ ——信号波长；

$c$ ——信号在 PCB 上传输的速度，该速度略低于光速，与信号走线所在的层有关，为讨论方便起见，此处将  $c$  视为常数；

$F$ ——信号的频率。

在  $c$  为常数的前提下， $\lambda$  与  $F$  成反比，即信号频率  $F$  越高，其波长越短，则低速和高速分水岭的信号线长度越短，反之亦然。

因此，在信号频率已知的前提下，可以确定低速和高速分水岭的信号线长度。显然，根据前面的讨论，此处的信号频率应采用信号的有效频率  $F_{knee}$  而不是信号的周期频率  $F_{clock}$ 。

综合上述，区分高速和低速信号的步骤如下：

第一步，获得信号的有效频率  $F_{knee}$  和走线长度  $L$ 。

第二步，利用  $F_{knee}$  计算出信号的有效波长  $\lambda_{knee}$ 。

第三步，判断  $L$  与  $1/6 \times \lambda_{knee}$  之间的关系，若  $L > 1/6 \times \lambda_{knee}$ ，则信号为高速信号，反之，则为低速信号。

在以上步骤中，需注意以下几点：

(1) 如何获得信号的有效频率  $F_{knee}$  呢？在有测试板等现成电路的情况下，可直接测量信号的 10%~90% 上升时间，再利用式 (1.2) 即可计算得到  $F_{knee}$  的值。而在没有现成电路的情况下，可假设信号的上升沿时间为信号周期的 7%<sup>[57]</sup>，此时，信号有效频率  $F_{knee}$  约为信号周期频率  $F_{clock}$  的 7 倍，例如，周期频率为 100MHz 的时钟信号，可估计其有效频率约为 700MHz。

(2) 第一点对极高频信号（如频率在 1GHz 以上的信号）并不成立，极高频信号的上升沿很缓，上升时间甚至可能达到信号周期的 20%，因此，再利用  $F_{knee}$  的计算公式已经没有意义，同时，判断极高频信号属于高速还是低速，本身也是一件没有意义的事情。

对所有的高速信号，应视做传输线处理，本书第 8 章将详细讨论传输线的应用及设计要点。

#### 理解要点：

- ① 信号的最高频率成分取决于其有效频率而不是周期频率。

- ② 高速电路设计中，电容、电感等都不是理想的器件。

- ③ 高速信号指传输路径上各点电平存在较大差异的信号。高速与低速的区别，不仅取决于信号频率，还取决于信号传输路径的长度。

- ④ 信号频率越高，则低速和高速分水岭的信号线长度越短，反之亦然。

## 1.3 硬件设计流程

高速电路设计属于硬件设计，对从事高速电路设计的工程师而言，需掌握从需求分析到大规模生产的各个环节。本小节将简单地对这些环节进行介绍，本节内容虽不针对高速电路设计，但却是高速电路设计者必须了解的。

硬件设计的流程分为以下几个步骤：需求分析、概要设计、详细设计、调试、测试、转产。

### 1.3.1 需求分析

需求分析是硬件设计的第一步，也是最关键的一步。在需求分析阶段，只有充分地理解了客户的需求，才能有针对性地开展器件选型、方案规划等工作。

需求的种类很多，与硬件开发相关的有以下几类。下文以某以太网产品的需求分析为例，进行简单的介绍。

(1) 整体性能要求：如数据包转发能力、处理延时、最高处理带宽、CPU 处理能力等。针对这些要求，可初步进行 CPU、存储器、交换芯片等器件的选型。

(2) 功能要求：如 QoS (Quality of Service，服务质量)、各类以太网相关协议的实现等。针对功能要求，可对多个厂家提供的交换芯片等器件做进一步细分，筛选能满足所有功能要求的器件。

(3) 成本要求：成本分析是需求分析中重要的一步，在满足客户需求的前提下，尽可能地降低成本，是硬件工程师的重要职责。在成本的分析中，应计算各套方案下单板的总成本，在某些场合，还需计算单个用户接口的成本。例如，某客户提出的需求是 1000 个以太网接口，针对该需求，提出了两套方案，分别是单块业务板提供 24 和 48 个接口，相对前者，后者对 CPU 和存储器的要求比较高，在这种情况下，计算单个接口的成本比计算整个单板的成本更有意义。

(4) 用户接口要求：如接口的种类、数目，指示灯及其规范、复位键、电源按钮等。同时，该类需求还包括与用户操作相关的要求，如对单板状态的在线监控等。这类要求多着眼于细节，不大会影响关键器件的选型，但若忽略了其中的某一项，即可能导致整个产品的失败。例如，某产品的用户面板上提供有主、备两个串口，分别标识为“Master”和“Slave”，由于“Slave”在英文中有奴隶的含义，违反了某些地区对电子产品标识的规定，导致该产品在这些地区无法销售。

(5) 功耗要求：功耗要求是单板上电源功率分配的依据，涉及电源架构的设计、电源电路器件的选型。

某以太网产品的需求分析报告如表 1.1 所示。

表 1.1 某以太网产品的需求分析报告

|            | 方案 1     | 方案 2      | 方案 3     |

|------------|----------|-----------|----------|

| 接口种类与数目    | 24 个千兆口  | 48 个千兆口   | 24 个千兆口  |

| CPU        | MPC850   | MPC8360   | MPC850   |

| 存储器        | 64MB     | 512MB     | 128MB    |

| 二、三层交换     | 支持       | 支持        | 支持       |

| QoS        | 4 个优先级队列 | 16 个优先级队列 | 8 个优先级队列 |

| MAC 地址学习能力 | 4096 个   | 16384 个   | 8192 个   |

| 数据转发延时     | 高        | 低         | 中        |

| 总功耗        | 96W      | 150W      | 105W     |

| 总成本        | 960 美元   | 2160 美元   | 1008 美元  |

| 单口功耗       | 4W       | 3.125W    | 4.375W   |

| 单口成本       | 40 美元    | 45 美元     | 42 美元    |

针对表 1.1，补充说明一点，表中所计算得到的单口成本并未考虑机框、用户机房占用面积的成本，方案 1 和方案 3 的单口成本低于方案 2，但方案 2 中，单块单板拥有更多的接口数目，因此，相对另外两种方案，更能节省机框和机房面积的成本，在这种情况下，又需要结合总成本来考虑。

需求分析阶段的工作是制定设计的大方向，不能忽略细节，但也不能拘泥于细节。需求分析阶段的工作并不是哪一个特定工程师的工作，而应由项目经理、系统工程师、电子设计工程师、软件工程师、逻辑工程师等协作完成。

### 1.3.2 概要设计

从概要设计阶段开始，软件、硬件工程师开始分头工作，本小节只讨论硬件方面的工作。

硬件概要设计的主要任务是设计系统框图、关键链路连接图、时钟分配框图等，并制定电源设计总体方案，对信号完整性及 EMC 的可行性、结构与散热的可行性、测试可行性等环节，做初步的分析。在这一阶段，需要电子设计工程师、电源工程师、信号完整性工程师、结构与热设计工程师、EMC 工程师、测试工程师等协同工作。

需求分析的目标是选定一套最佳的方案，确定关键器件及总体架构，而概要设计则是对该架构做进一步的细化，在概要设计阶段，与硬件设计相关的各部门工程师开始介入并做可行性分析，若发现总体方案的某些方面不可行，应回馈给项目经理，重新进行需求分析，并更改方案。因此，可以认为，需求分析和概要设计这两个阶段是螺旋形前进并不断反复的过程。

### 1.3.3 详细设计

概要设计完成后，单板的总体框架已经确定，则在详细设计阶段需要完成的工作是，基于该框架，将每一个部分细化。以下简要地介绍各职能部门工程师的职责。

#### 1. 电子设计工程师

电子设计工程师负责各个总线接口信号的定义，CPU 存储空间分配，时钟、复位电路器件选型及其拓扑结构，中断链路拓扑结构，电源电路的详细框图（需注明各路电源的产生方式、电压值、电流值等），关键电源的滤波方式，逻辑器件功能及其寄存器说明书，面板上用户接口的定义及接口信号连接关系，指示灯器件的选型及其连接关系，最后绘制原理图并产生物料清单。在详细设计阶段的后期，应开始测试计划的制订。

#### 2. PCB 设计工程师

根据电子设计工程师提供的原理图及对应的网表，结合信号完整性工程师提供的走线规则和层叠结构，完成 PCB 的设计，并生成可供工厂生产使用的文件。

#### 3. 信号完整性工程师

根据电子设计工程师提供的详细设计文档，同时根据板内高速信号的信号质量及时序要求，设计 PCB 层叠结构，基于前仿真的结果定义信号的走线规则，在 PCB 走线完成

后，对高速信号进行后仿真以初步验证信号完整性，对关键电源做电源完整性仿真，向电子设计工程师提供关于电源滤波的参考意见，最后协同电子设计工程师，共同完成测试计划的制订。

#### 4. 逻辑设计工程师

根据电子设计工程师提供的逻辑器件说明书，编写逻辑器件的代码及测试代码，并进行相关的仿真。

#### 5. 电源设计工程师

根据电子设计工程师提供的各关键器件的电源电压及电流值，汇总得到各类电源的总功耗需求，根据该结果，进行电源器件的选型及电源架构的设计。同时，对较复杂的电源电路，电源设计工程师还应给出推荐的电源电路和滤波方案。在调试和测试阶段，电源设计工程师负责协助电子设计工程师完成电源电路的调试与测试。在电源电路不是特别复杂的情况下，往往由电子设计工程师兼任电源设计工作。

#### 6. 结构工程师

根据电子设计工程师提供的用户面板信息以及 PCB 设计工程师提供的 PCB 尺寸、定位、安装等信息，设计 PCB 的机械图，制定 PCB 的限布区（禁止布放器件的区域）和限高区（禁止布放超高器件的区域），在 PCB 上设定安装孔的位置，同时还负责面板的设计。这些设计图和数据将成为 PCB 设计的重要输入信息。

#### 7. 热设计工程师

根据电子设计工程师提供的各器件总功耗，器件布放位置及器件的高度，进行热方面的仿真，结合仿真结果完成热设计，如散热片的选型、风道的规划、温度传感器的布放位置等。同时，热设计工程师应将单板的温度散布区域图提供给电子设计工程师，以作为 PCB 布局的参考。

#### 8. EMC 及防护设计工程师

根据电子设计工程师提供的用户接口信息、高速信号的速率和分布区域，以及 PCB 设计工程师提供的 PCB 层叠结构，定义高速信号走线规则，用户接口防护方案等。需要说明的是，信号完整性工程师和 EMC 设计工程师都会对高速信号的走线规则做出定义，两类走线规则可能会有冲突，此时应由电子设计工程师负责与这两位工程师协商，确定最终的规则。

#### 9. 测试工程师

测试工程师包括边界扫描设计工程师、ICT 工程师（ICT 指在线测试，将在第 8 章介绍）、硬件测试工程师。前两类有专门的职能部门，一般不由其他工程师兼任，而硬件测试工程师往往可以由电子设计工程师兼任。

边界扫描设计工程师和 ICT 工程师根据电子设计工程师提供的原理图、器件资料，前者负责完成边界扫描链路的设计和程序的编写，后者负责完成 ICT 夹具的设计和程序的编

写。需注意，由于 ICT 夹具的制作成本较高，在硬件设计稳定之前，一般不会完成夹具的设计，因此对一块新设计的单板而言，在前几版的生产中，一般无法使用 ICT 测试。

硬件测试工程师根据电子设计工程师提供的原理图，进行可测试性分析，汇总需要测试的信号，并辅助 PCB 设计工程师，为各信号添加测试点。

### 10. 产品工程师

产品工程师是设计部门与生产部门沟通的纽带。根据电子设计工程师提供的物料清单，产品工程师检查各器件的厂家生产状况、生产部门备料情况，做出更换、推荐器件的建议，并将结果反馈给电子设计工程师。PCB 设计完成后，产品工程师负责检查 PCB 设计是否符合可生产性、可加工性的规定，对违反规定的部分，提出修改建议，并反馈给 PCB 设计工程师。

### 11. 软件工程师

在这一阶段，软件工程师应开始软件的详细设计，但同时，还应与电子设计工程师协同工作，确定 CPU 速率、复位逻辑、中断拓扑、各器件之间的互连接口、用户监控等信息，以使软件设计与硬件设计相匹配。

由以上职责描述可知，在硬件详细设计阶段，电子设计工程师除负责电路设计外，同时在各部门间还发挥了协调的作用。电子设计工程师的输出，将作为其他各部门的输入，而其他各部门的输出，又成为电子设计工程师的输入，环环相扣。因此可以说，一个成功的硬件设计是一个有机的整体，需要多部门工程师的协调工作，任何一个环节出错都可能导致整个设计的失败。

## 1.3.4 调试

单板从工厂生产加工完成后，回到研发部门，由电子设计工程师、逻辑设计工程师、电源设计工程师、软件工程师协同进行调试。

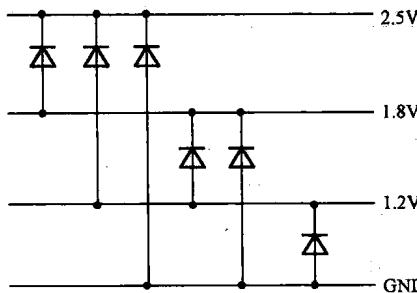

对第一次回到研发部门的单板，首先需要做的是验证是否存在电源短路现象。例如，某块单板有以下几种电源：3.3V、2.5V、1.8V、1.2V，则调试阶段的第一个步骤就是验证这些电源是否与 GND（单板上的信号地）发生了短路，以及各电源之间是否发生短路。对电源保护设计不完善的单板，这一步骤尤为重要。

第二个步骤是对单板上可编程器件程序的加载。

其后，对电源电路、逻辑设计、时钟和复位电路等功能模块的调试可并行进行。

当以上功能模块的调试通过后，可开始测试流量。流量测试是验证单板上各部分电路协调工作的最佳工具，在这一步，除长时间正常流量的测试外，还需人为地模拟一些可触发中断等告警功能的流量，以对相应功能模块进行验证。

## 1.3.5 测试

测试是对设计进行验证的重要阶段。硬件测试工程师是这一阶段的主要负责人，其关键输入为详细设计阶段后期电子设计工程师拟定的测试计划。

## 1. 测试计划的主要内容

- (1) 测试设备列表。列出测试中所需仪器的型号和数目，如电源、示波器、探头、万用表、信号发生器等。

- (2) 测试环境的搭建图。绘制测试仪器与被测单板的连接示意图，若测试中需要以太网口、串口等线缆的连接，示意图中还需标明线缆的规格、线缆连接的方式及对应端口的地址。

- (3) 电源测试。测试各电源的电压及电流（针对空载和满载两种情况）、纹波、噪声、上电顺序、下电顺序。

- (4) 各接口信号的信号完整性与时序。在测试计划中，应列出待测信号的网络名、时序要求等。

- (5) 各通用接口的功能测试：通用接口指 I<sup>2</sup>C、RS-232 等标准接口，在测试计划中应列出各接口的访问地址及测试代码。

- (6) 复位链路的测试。

- (7) 晶振、时钟驱动器、锁相环等与时钟相关的测试。测试时钟信号的频率、上升/下降边沿时间，对关键时钟信号，还应借助温箱，测试环境温度变化时时钟频率的稳定度。需注意，不推荐利用示波器测试时钟频率，而应采用专门的频率测试仪进行测试。

- (8) 指示灯、单板在位信号、槽位号等杂项的测试。

- (9) 流量的测试。测试计划中应列出流量测试的数据流向图，测试代码、测试时间、误码率要求等。

## 2. 其他测试

除以上常规测试外，在测试计划中还需包括某些强度测试的测试项。不同类型的单板有不同的强度测试项，以下仅举一些通用的例子。

(1) 电源监控功能的测试。例如，通过强制将电源电压调整超出监控的阈值，判断监控电路是否报警。

(2) 极限环境的测试。例如，调整板上电源输出电压到最高、最低极限值，调整温箱的温度变化率，在这些极限环境下对流量进行测试。

若单板上包括有某些特定用户接口，如以太网电口、光口，光传输的 E1、T1 等端口，都需要根据接口所对应的标准规范，验证接口是否满足规范的要求。

在测试阶段，硬件测试工程师的职责是按照测试计划书一项一项地测试，并将结果反馈给电子设计工程师，针对测试所发现的问题，提供相应的更改意见。

### 1.3.6 转产

在调试和测试完成后，硬件设计的最后一个阶段是将与生产相关的资料转给工厂，以便工厂开始大规模批量生产。

在这一阶段，ICT 工程师的测试夹具和代码也应完成并提供给工厂。此时，电子设计工程师的职责是将单板知识和测试技能传授给工厂的测试人员。

## 理解要点：

- ① 硬件设计流程包括以下几个阶段：需求分析、概要设计、详细设计、调试、测试、转产。

- ② 一个设计的成功，需要来自多个部门的工程师通力合作。

## 1.4 原理图设计

本书后续部分将详细介绍硬件设计流程的各个阶段。在此之前，本节将简单地介绍原理图设计时的注意事项。

原理图是电路设计的中间文件，虽然其并不直接用于指导生产，但却是连接设计理念和最终产品的关键纽带。

电子设计工程师是原理图的责任人，多数设计者认为原理图不过是生成网表的源文件，至于其设计风格则完全可以依个人喜好而定。

事实上，原理图在整个设计过程中，起着非常关键的作用。

首先，原理图是设计思想的体现，混乱的原理图只能代表混乱的设计思想。

第二，原理图是电子设计工程师与 PCB 设计工程师沟通的重要工具，当单板复杂到一定程度时，电子设计工程师不可能通过语言将所有 PCB 设计时需注意的细节都告知 PCB 设计工程师，例如，PCB 设计工程师从原理图获得网络连接关系表（简称网表），虽然知道各器件的连接关系，但却无法获得器件摆放位置等信息，在这种情况下，原理图的标注将成为重要的工具，一方面使 PCB 设计工程师对设计的要求一目了然，另一方面也能对电子设计工程师起到提醒作用，避免在设计、测试时遗忘某些关键细节。

第三，脉络清晰的原理图有助于提高调试、测试、生产等环节的效率。

由以上看来，原理图并不只是一份中间文件，为了得到一份优质的原理图，在设计的过程中，有许多事项需要注意。

(1) 在原理图的首页，应绘制单板的总体框架图。若单板较复杂，还应根据需要，在后续页上绘制电源架构框图、时钟拓扑图、复位链路拓扑图、中断链路拓扑图、边界扫描链路图等。若单板的面板接口较多，建议增加一页用于面板图示。若 I<sup>2</sup>C 总线的拓扑较复杂，还需增加一页用于注释各 I<sup>2</sup>C 器件的地址。

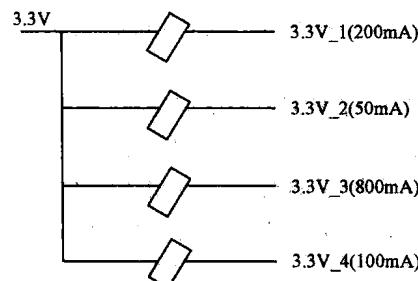

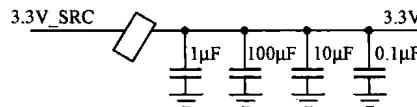

(2) 在原理图上电源电路的输出端附近，应标注该路电源的电压值和电流值。例如，图 1.3 中，由磁珠从 3.3V 分出四路 3.3V 的支路，各支路电流不同，在原理图上标注电流后，有助于 PCB 工程师把握在哪些支路应做加粗走线、增加电源过孔等处理。需说明的是，图 1.3 中括号包含的部分（如 200mA）只是注释，不属于网络名称的一部分。

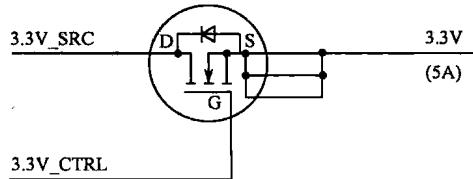

(3) 标注关键电流通路。例如，在图 1.4 中，MOSFET 的源极和漏极两端的路径属于关键电流通路，在原理图上标注后，有利于 PCB 设计者对该路径引起重视，做加粗走线等处理。

图 1.3 在原理图上标注各支路电源的电流值

注: 3.3V\_SRC与3.3V为电流关键路径

图 1.4 在原理图上标注关键电流通路

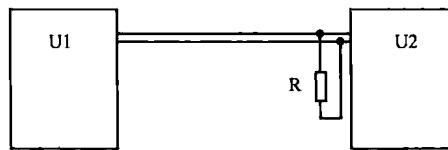

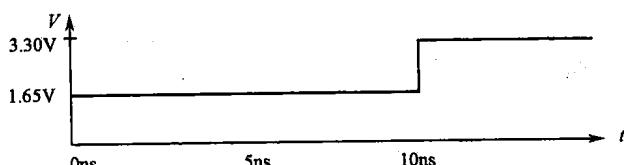

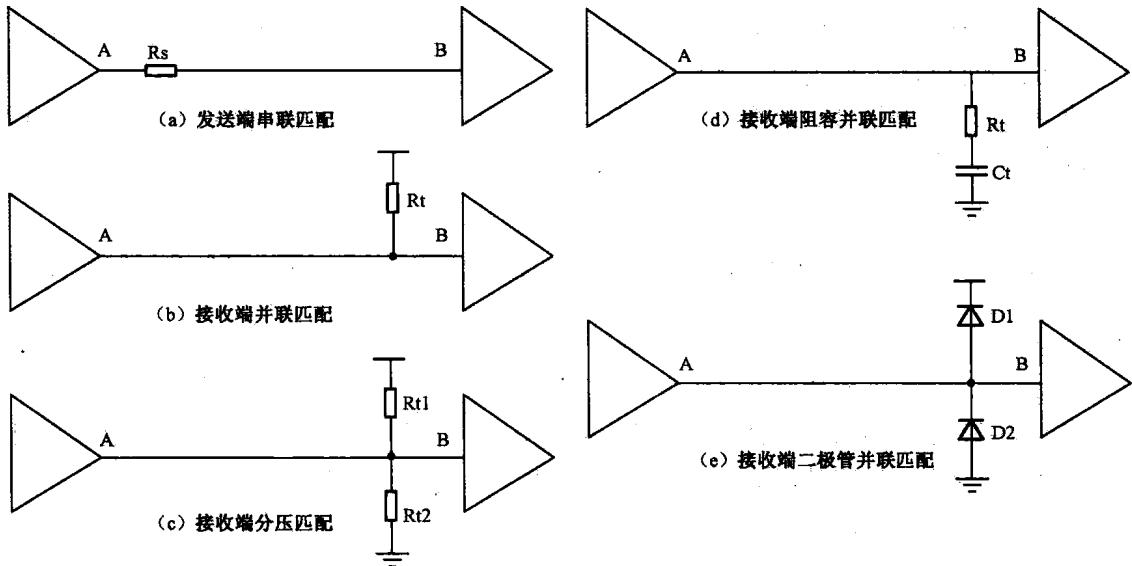

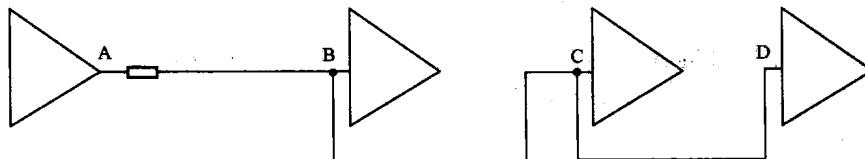

(4) 绘制原理图时要兼顾在 PCB 设计中对器件布放位置的要求。在第 8 章将介绍阻抗匹配, 阻抗匹配电路对器件的布放位置有一定的要求, 例如, 始端匹配电阻应靠近发送端器件放置, 终端匹配电路应靠近接收端器件放置, 在原理图的绘制中应体现这一原则。例如, U1 和 U2 分别为发送、接收器件, R 为终端匹配电阻, 在 PCB 上应靠近 U2 放置, 则推荐按图 1.5 方式绘制原理图。有时, U1 和 U2 位于原理图上不同的页, 则推荐将 R 放置在 U2 的那一页上。

图 1.5 原理图的绘制应兼顾 PCB 上器件的布放要求

(5) 按照 PCB 上电容的排列顺序绘制原理图的电容滤波电路。某 3.3V 滤波电路要求, 在 PCB 上,  $1\mu\text{F}$  电容应放置在最外边, 随后是  $100\mu\text{F}$ 、 $10\mu\text{F}$ 、 $0.1\mu\text{F}$ , 则对应的原理图部分应绘制如图 1.6 所示。

图 1.6 原理图兼顾电容的布放顺序

(6) 原理图上应标注关键信号的速率、走线层, 若信号线之间有走线长度关系, 也建议标注在原理图上。

(7) 原理图上应标明高散热及热敏感器件, 若有特殊的放置要求, 也可在原理图上加以注释。

(8) 对关键器件, 在原理图上应标明其对应的料号、精度、尺寸等信息。这些关键器件包括保险管、分压电路中的电阻, 电源滤波电路中的电感、磁珠、电容, 电源电路中的电压及开关频率调节电阻、MOSFET、二极管、电压采样电阻等。

(9) 在原理图上, 应对跳线、选焊器件的配置方法等进行注释。

(10) 在原理图上, 应标注与背板连接的连接器、面板上 LED 指示灯的排列顺序。

# 第2章 高速电路中的电阻、电容、电感和磁珠的选型及应用

## 2.1 电阻的应用

### 2.1.1 与电阻相关的经典案例

如果说芯片是电路的骨架，那么电阻就是在芯片之间起连接作用的关节。电阻的阻值、布放位置等，对设计的成功起着至关重要的作用。

#### 【案例 2-1】 串联电阻过大，导致板间告警失败

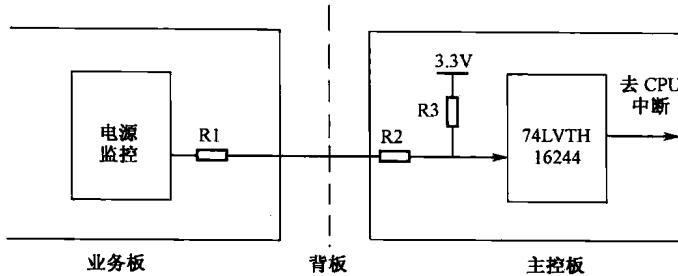

某产品由业务板和主控板构成。业务板上电源监控芯片的告警信号通过背板，输送到主控板，经主控板上逻辑芯片 74LVTH16244 处理后连接到主控板上 CPU 的中断信号。

功能测试发现，强制将业务板被监控的一路电源拉地，CPU 中断信号却不被使能。

#### 【讨论】

该部分电路如图 2.1 所示。

图 2.1 业务板与主控板之间的告警电路

考虑到单板的热插拔要求，信号和背板连接器之间都串有电阻。 $R_1=1\text{k}\Omega$  ( $\text{k}\Omega$ : 千欧姆)， $R_2=100\Omega$  ( $\Omega$ : 欧姆)， $R_3=1\text{k}\Omega$ 。

进行强度测试时强制将被监控的电源接地，在业务板侧，测量业务板电源监控芯片输出的告警信号，可测得有效低电平 (0V)，但在主控板 74LVTH16244 侧，测得输入信号电平为 1.7V，远超出低电平的输入门限。

74LVTH16244 是高阻抗输入，因此 3.3V 将在三个电阻上分压。当电源监控芯片输出低电平 0V 时，经过分压后，在主控板上 74LVTH16244 的输入端分得电平为  $\frac{3.3\text{V}}{2.1\text{k}\Omega} \times 1.1\text{k}\Omega = 1.7\text{V}$ ，超出低电平门限。将  $R_1$  的阻值更换为  $33\Omega$ ，告警时 74LVTH16244

输入电平为  $\frac{3.3V}{1.133k\Omega} \times 0.133k\Omega = 0.38V$ ，仍在低电平门限之内，主控板能正确识别告警信息。

这个案例看似简单，但却暴露出一个多单板协同设计时很容易出现的问题。在本案例中，考虑到热插拔需要，单独看主控板和业务板的设计都不存在缺陷，但在协同工作时却暴露出问题。若一个产品由多块单板组成，设计者在进行单板与背板连接器接口电路设计时，必须充分考虑本单板与其他单板协同工作的问题。

需要提及的是，有些设计者会有疑问，将 R1 的阻值改为  $33\Omega$  后，74LVTH16244 输入电平  $0.38V$  虽然处在输入信号的低电平门限范围内，但裕量不是很大，能不能将 R3 的阻值增大，如采用  $4.7k\Omega$  等，使得告警时 74LVTH16244 输入电平进一步降低？答案是不能，这涉及逻辑器件实现电平翻转时的电流要求，将在第 3 章做详细分析。

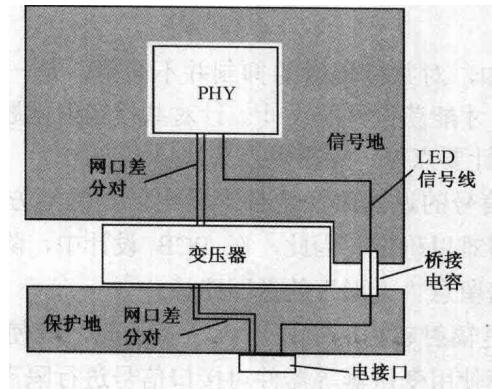

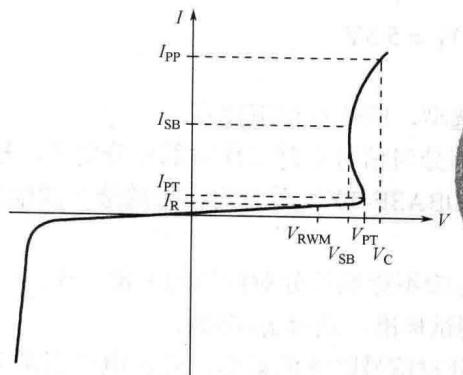

### 【案例 2-2】 电阻额定功率不够造成的单板潜在缺陷

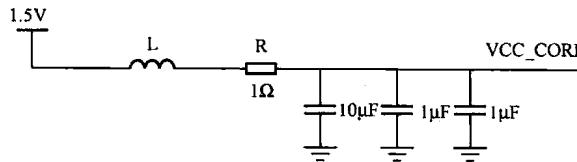

某单板上 PHY 芯片（以太网物理层芯片）的核心电源滤波电路设计如图 2.2 所示。

图 2.2 PHY 电源滤波电路

根据 PHY 芯片资料，该电源对噪声等干扰特别敏感，因此在设计中不仅采用了 LC 滤波电路，还在电感 L 之后串联了一个  $1\Omega$  的电阻 R。LC 滤波电路能滤除高频段噪声，而本电路中的电阻 R 不仅能衰减高频段噪声，而且能衰减低频段噪声，即能作为一个全频段衰减器。这种设计方法常用于对噪声特别敏感的电源，如时钟的电源等。

单板长时间运行发现，电阻 R 经常爆裂。

### 【讨论】

设计中选用的电阻 R，尺寸为 0402，额定功率为  $1/16W$ ，核对 PHY 芯片资料，其内核电源最大功耗为  $300mW$ ，即最大电流为  $200mA$ ，而该电阻的最大通流能力仅  $62.5mA$ 。当 PHY 全速工作时，电流将超过电阻的额定电流，造成电阻失效。

类似的案例很多，设计者在电阻选型时，对阻值往往非常关注，却比较容易忽略对额定功率的审核。

本案例中，电阻的失效能通过实验室长时间测试反映出来，这是很值得庆幸的事情。若电阻的额定电流和实际工作电流比较接近，则可能构成产品的一个潜在缺陷。

### 【拓展】

在本案例中，电阻起的是全频段滤波的作用，在类似应用中，电阻还有一个作用是降低电路的品质因数 Q。

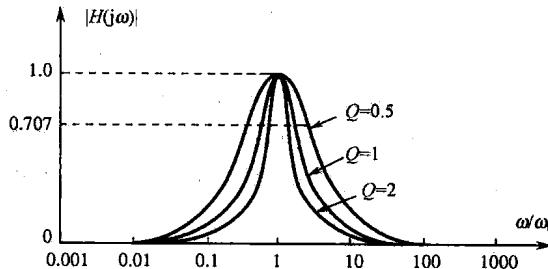

Q 定义为回路发生谐振时，储存能量与一周期内消耗能量之比。在一个由 R、L、C 组成的串联电路中，总阻抗  $Z = R + 1/(j\omega C) + j\omega L = R + j[\omega L - 1/(\omega C)]$ ，回路谐振时，假定谐振频率为  $\omega_0$ ，则满足  $\omega_0 L = 1/(\omega_0 C)$ ，此时电路的总阻抗达到最小值 R，Q 的值如下：

$$Q = \omega_0 L / R = 1 / (\omega_0 C R) = 1 / R \times (L/C)^{1/2} \quad (2.1)$$

因此，回路发生谐振时，能量将集中于谐振频率点  $\omega_0$ 。根据  $Q$  值的不同，绘制回路幅频特性曲线如图 2.3 所示，图中  $|H(j\omega)|$  是电路传递函数的模，该值越接近 1，表示电路越能无损耗地传递能量。从图中可以发现， $Q$  值越大，能量越集中，表现为  $|H(j\omega)|$  的值越接近 1，电路的损耗越小。

图 2.3 不同  $Q$  值的幅频特性曲线

在储能电路中， $Q$  值越大，意味着损耗越小；在选频电路中， $Q$  值越大，意味着滤除其他频带信号的能力越强。因此在这些情况下，希望  $Q$  值越大越好。

但在电源或信号线路中， $Q$  值越大，通频带内特性曲线越陡峭，越容易引发振铃等现象，信号通过这种回路后容易发生失真。因此在这种情况下，希望  $Q$  值小一些比较好。

在本例所示的原理图中，加入电阻 R 可降低  $Q$  值，以避免电源线路的振荡。

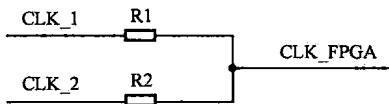

### 【案例 2-3】 电阻在时序设计中的妙用

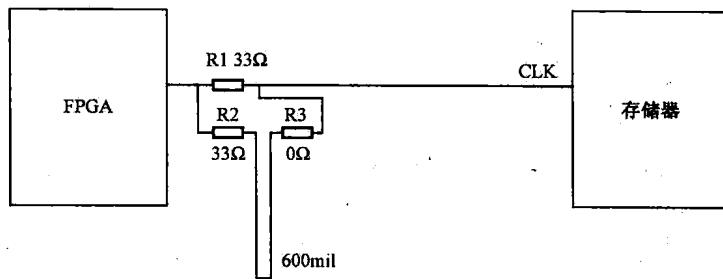

某设计要求 FPGA 芯片兼容地支持两个厂家的存储器，经时序分析发现，这两个厂家的存储器虽然引脚的定义完全相同，但时序参数却略有差异。经时序计算后，B 厂家存储器件的时钟信号线要比 A 厂家的长 600mil（mil 即米尔，是长度单位，1mil=0.0254mm）。

#### 【讨论】

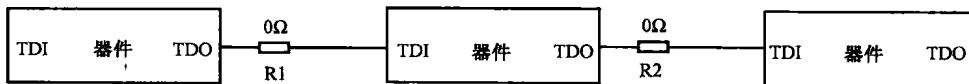

一个设计（即同一份原理图和 PCB）同时兼容两个厂家的器件，是电路设计中常见的需求，此时， $0\Omega$  电阻往往能起到极好的作用。

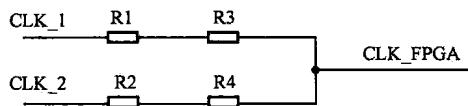

如图 2.4 所示，当采用 A 厂家存储器时，将 R1 加入物料清单中，而 R2 和 R3 不入物料清单；当采用 B 厂家存储器时，R2 和 R3 加入物料清单，而 R1 不入物料清单。

图 2.4 FPGA 兼容两种存储器的设计

PCB 设计的注意事项有：第一，R2 需紧紧靠近 R1 的左边引脚放置，R3 需紧紧靠近 R1 的右边引脚放置，这样做的目的是减少在时钟信号线上可能出现的分叉（stub）；第二，

R2 和 R3 之间的走线长度为 600mil，以满足 B 厂家存储器的时序要求。

如果信号速率极高，短小的分叉将对信号完整性产生很大的影响，因此，当设计不允许信号线上存在分叉时，可以采用如图 2.5 所示的 PCB 设计。

图 2.5 无分叉的兼容性设计方法

在图 2.5 中的 PCB 上，将 R2 和 R3 各自的一个引脚焊盘与 R1 的两个引脚焊盘分别重合，R2 和 R3 的另一个引脚通过 600mil 走线连接，从而可以完全避免在 R1 与 R2、R3 之间存在的分叉。采用这种方式，PCB 上将出现设计规则检查（DRC）错误，可以将这个错误忽略，并通知产品工程师。

## 2.1.2 电阻应用要点

在高速电路设计中，对于电阻的应用，有四个关注点：

- (1) 电阻的阻值；

- (2) 电阻的尺寸；

- (3) 电阻的额定功率；

- (4) 电阻的精度。

其中，对于阻值，可依据电路的要求计算得到。有时候计算得到的阻值属于非常用阻值，从节省成本的角度考虑，建议采用常用阻值的电阻通过串联或者并联的方式构成该阻值。例如， $363\Omega$  的阻值，可采用常用阻值  $330\Omega$  和  $33\Omega$  串联构成。这样做的目的，一方面可以构建比较精确的阻值，另一方面可以避免选用非常用的电阻器件。一般而言，越是非常用的器件，价格往往越高。

对于尺寸，需注意电阻的厂家资料上往往提供有两种尺寸代码，如表 2.1 所示。

表 2.1 电阻元件资料上的尺寸信息

| Item (项目)        | General Specification (技术规范) |            |            |

|------------------|------------------------------|------------|------------|

| Series No (系列号)  | WR12                         | WR08       | WR06       |

| Size code (尺寸编号) | 1206(3216)                   | 0805(2012) | 0603(1608) |

表 2.1 摘自某电阻的厂家资料。表中同一系列的电阻有两种尺寸代码，一种是 EIA（美国电子工业协会）代码，另一种是公制代码。这两种代码都由 4 位数字构成，前两位表示电阻封装的长度，后两位表示宽度。EIA 代码是英制代码，以英寸为单位，如 0603 的电阻，表示长度为 0.06in (60mil)、宽度为 0.03in (30mil)。该电阻的公制代码为 1608，表示长度为 1.6mm，宽度为 0.8mm。

额定功率和精度这两项参数比较容易被忽略。案例 2-2 就是与额定功率相关的案例，在针对额定功率的选型时，需要注意至少降额 20% 使用。

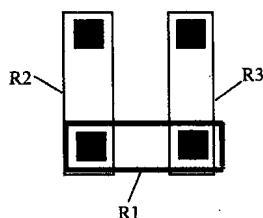

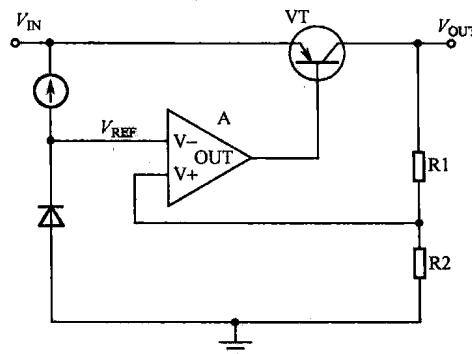

关于精度，最常见的应用是在电源芯片上。如图 2.6 所示为 Linear 公司的 LDO 电源芯片 LT3080，利用外部的电阻  $R_{SET}$  设定  $V_{OUT}$  的值。

图 2.6 LT3080 应用电路<sup>[5]</sup>

在这种应用中，电阻的精度直接决定了输出电压的精度，如果选择 5% 精度的电阻，则输出电源的电压波动范围将达到 10%，显然无法满足设计的要求，因此必须选择 1% 精度的电阻，即使这样，仅仅因为该电阻的精度偏差，输出电源的电压偏差就达到了 2%。

#### 理解要点：

- ① 0Ω 电阻对高速电路设计有重要的意义。

- ② 在功耗高的路径上，如果串联了电阻，选型时需要考虑电阻的额定功率。

- ③ 当电阻用于设定器件的工作参数时，应选择高精度电阻。

## 2.2 电容的选型及应用

### 2.2.1 与电容相关的经典案例

电容对高速电路的贡献非常大，即便是在一块最普通的单板上，电容也随处可见。因此，电容是电路设计中最为常见的器件。但同时，电容也是最容易被忽视的器件。在设计中，设计者们往往知道需要放置电容，但对电容的选型却随心所欲。

事实证明，很多单板的设计失败，根本原因就在电容。以下根据实际工作中的三个案例来说明电容选型的重要性。

#### 【案例 2-4】 电容失效导致低温下硬盘停止工作

某单板设计以及功能验证完成后，在温箱里做 -30℃ 的低温冷启动测试，发现单板启动到“硬盘检测”步骤时报错。在此条件下测试硬盘的 5V 电源，发现其纹波很大，达到 800mV，使硬盘无法正常工作。设计人员重新审视原理图后发现，在硬盘的 5V 电源上除了若干小容值的陶瓷电容以外，大容值的电容只有一个，是 47μF 的铝电解电容，该电容的工作温度范围为 -55℃ ~ 105℃。将此铝电解电容更换为同样容值的钽电容后，在 -30℃ 做多次低温冷启动，单板工作正常。

### 【案例 2-5】多次带电插拔子板导致母板上钽电容损坏

在调试中，对某单板上的子板做多次热插拔功能测试，发现插拔十多次就会导致母板上的一颗钽电容爆裂。该单板由母板和子板构成，两者通过连接器连接。由母板提供 12V 电源，经过连接器后送到子板，作为子板的工作电源，而该钽电容是母板上靠近连接器就近布放的、为 12V 电源滤波的电容，其标称值是  $100\mu\text{F}$ ，额定电压 16V。将该电容更换为同样容值的铝电解电容后，问题得到解决，强度测试通过。

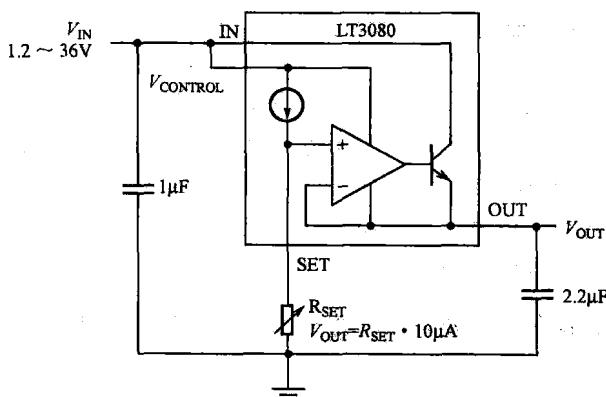

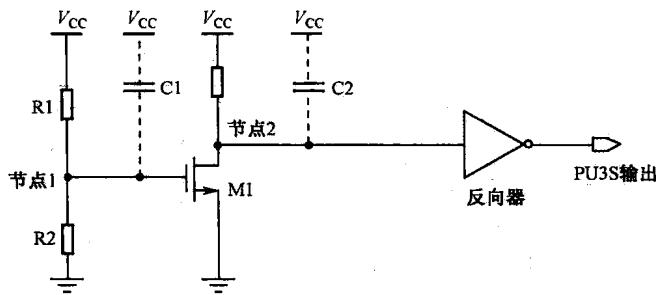

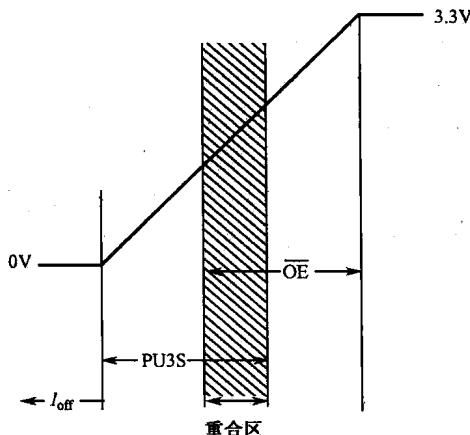

### 【案例 2-6】高速电路中电容应用问题导致 CPU 工作不稳定

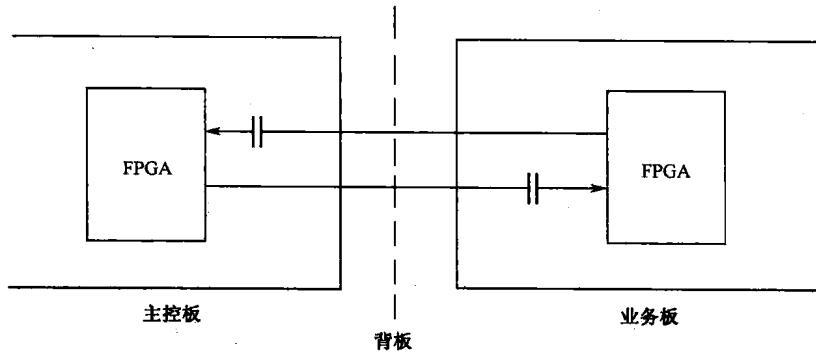

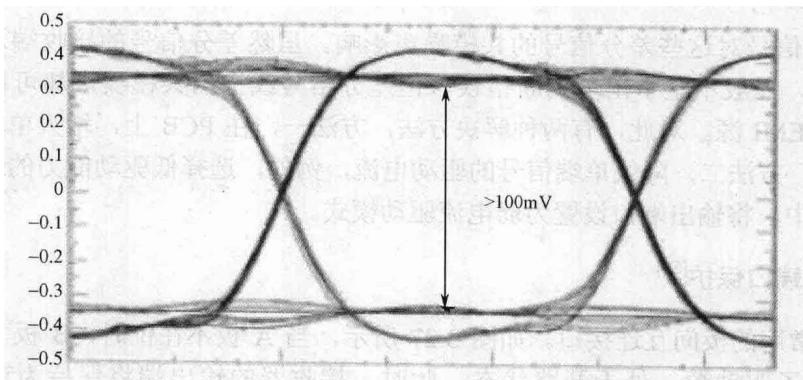

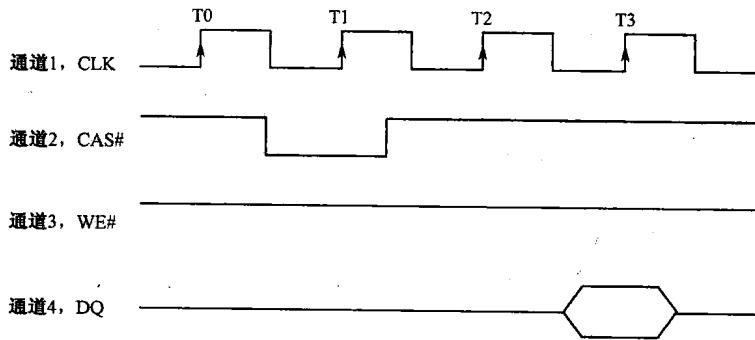

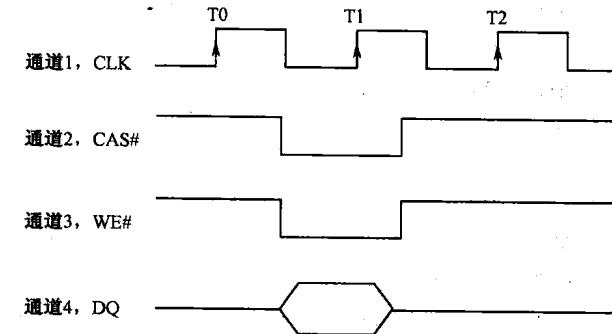

某单板上，以太网数据包的处理工作由 CPU 负责完成。测试发现，在少量数据处理时，单板工作正常，而一旦出现大量数据处理，偶尔会发生丢数据包现象。以太网数据是通过板上 FPGA 进行预处理后再送到 CPU，简化原理图如图 2.7 所示。

图 2.7 电容导致 CPU 工作不稳定

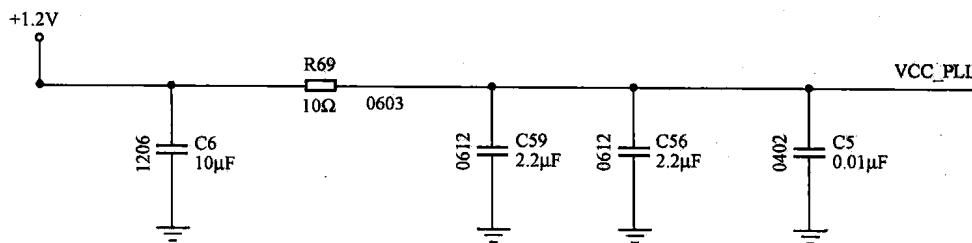

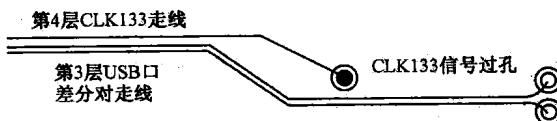

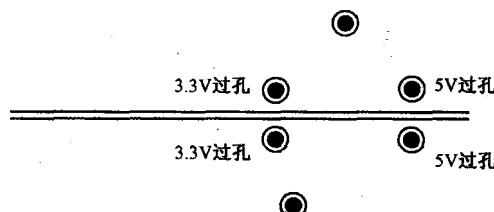

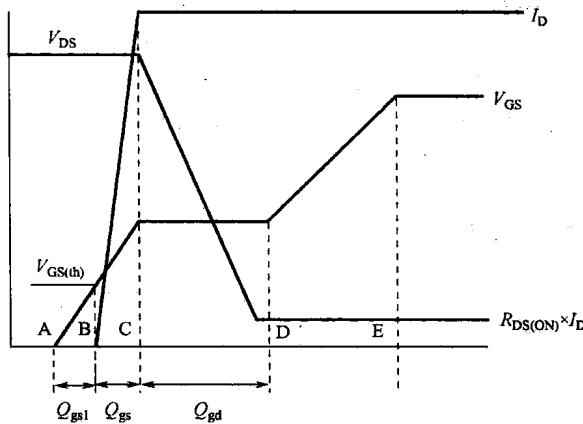

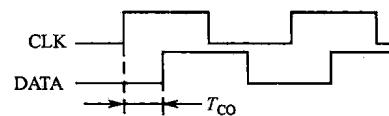

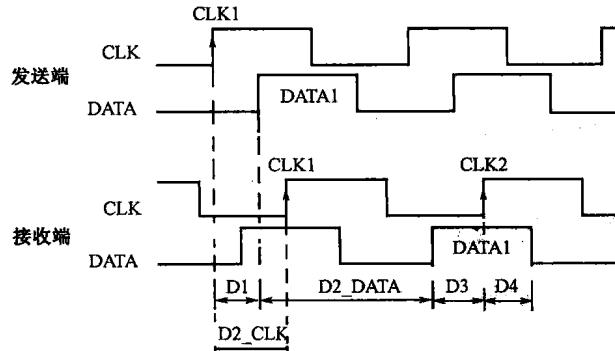

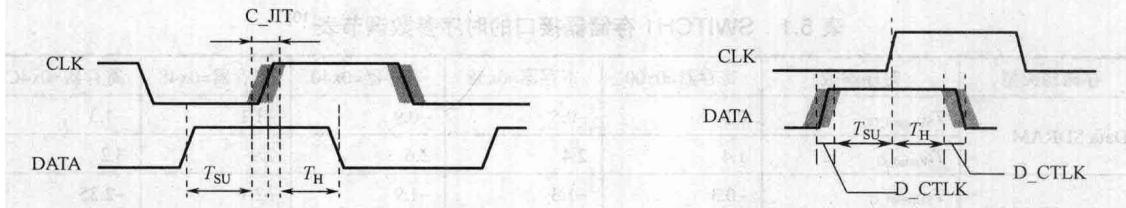

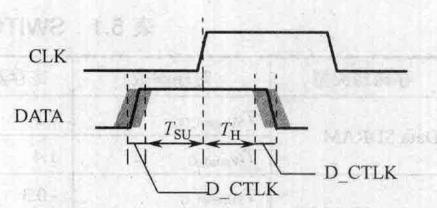

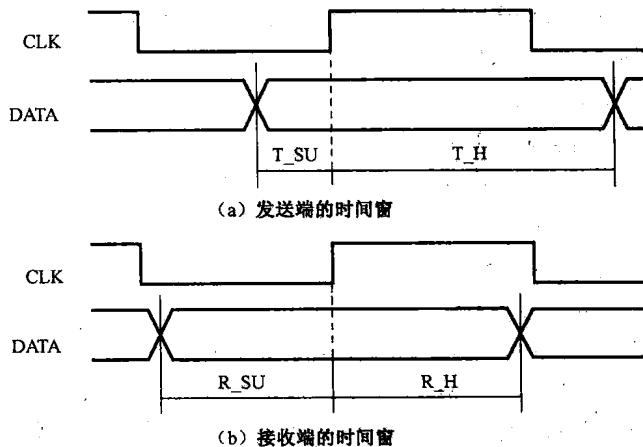

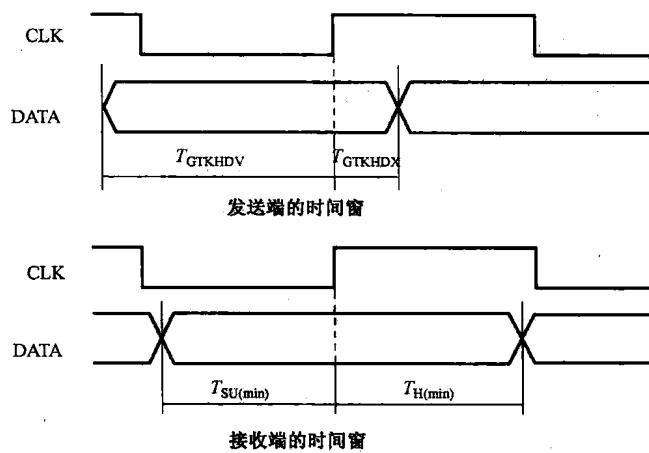

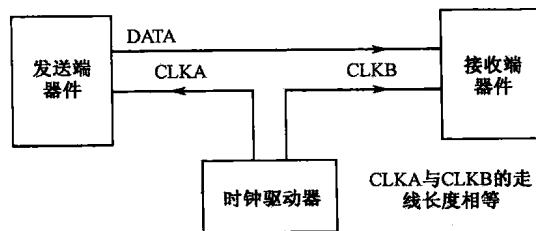

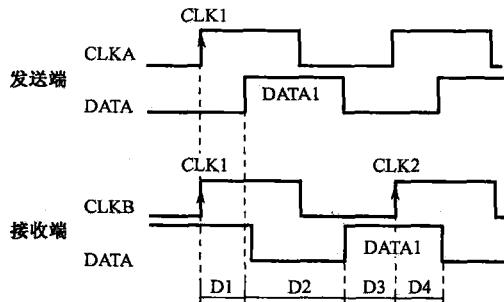

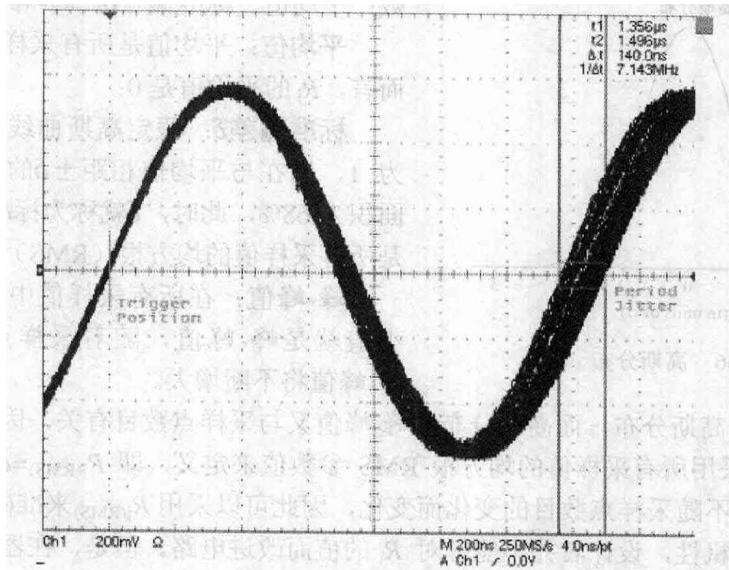

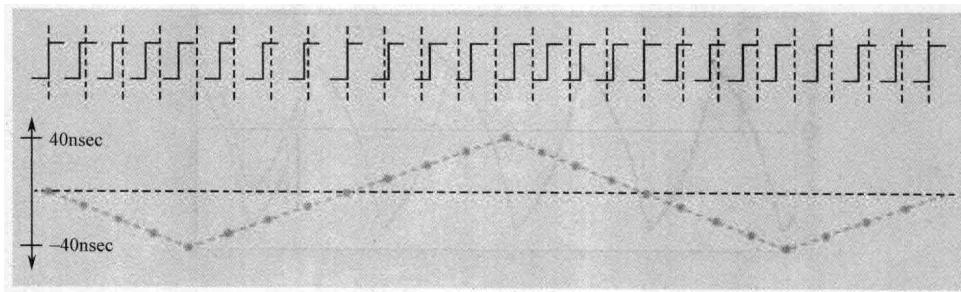

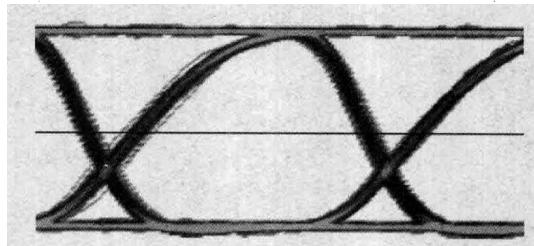

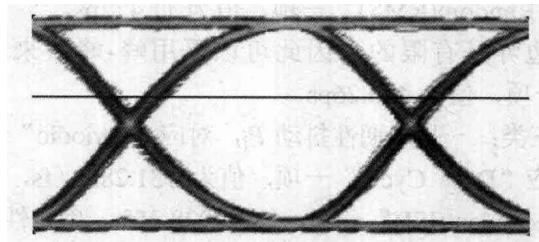

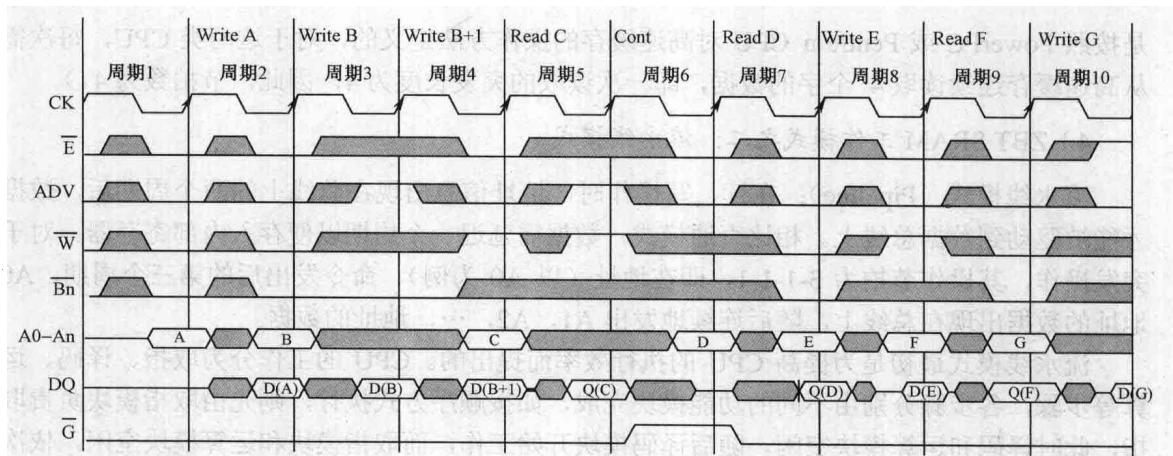

SYSCLK 是 CPU 的系统时钟，频率为 66MHz，由外部 66MHz 晶振提供。CLK 为 CPU 和 FPGA 之间接口总线的工作时钟，频率为 132MHz，由 CPU 内部锁相环对 SYSCLK 倍频产生。通过对 CPU 和 FPGA 之间的总线进行信号质量以及时序测试，大量数据处理时，借助示波器的快速采集功能，可以发现 FPGA 一侧的输入数据在某些瞬时无法满足时序要求，而大多数情况下却有充足的时序裕量。重新分析时序，发现时序设计正确。用示波器单独测量 CLK 信号的完整性，打开快速采集功能，发现在某些瞬间，CLK 信号的边沿会发生 1/4 周期的偏移。由此怀疑 CPU 内部的锁相环工作不稳定，测量给锁相环供电的 VCC\_PLL 引脚，纹波达到 50mV，纹波加上噪声达到 70mV。该电路设计时，VCC\_PLL 信号上仅布放有一个  $10\mu\text{F}$ 、1206 封装的陶瓷电容，改版后在 VCC\_PLL 引脚附近就近增加两个 0612 封装的  $2.2\mu\text{F}$  陶瓷电容，和一个 0402 封装的  $0.1\mu\text{F}$  陶瓷电容，问题得到解决。

类似的案例还有很多，表面上看都不违背电路原理。案例 2-4 中的铝电解电容，标称温度范围能达到  $-55^\circ\text{C}$ ，为何在  $-30^\circ\text{C}$  就会出现问题？案例 2-5 中的钽电容，额定电压 16V，距离其工作电压 12V 还有 33% 的裕量，为何会出现爆裂？案例 2-6 中的偶发现象，经过长时间、大量信号测试后，却发现根源竟是几个电容。电容虽小，出现的问题却需要耗费大量的调试时间，那么在设计中，如何避免出现类似问题？本节内容将主要就电容的选型和应用要点展开讨论。

## 2.2.2 高速电路设计中电容的作用及分析

### 1. 高速电路设计中电容的作用

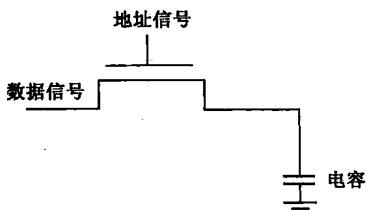

#### 1) 电容的作用之一——电荷缓冲池

在高速电路设计中，电源的负载是动态的，即高速运行器件的电流和功耗是不断变化的。为了保证器件工作的稳定，希望器件的工作电压不随电流和功耗的剧烈变化而同程度变化，即希望器件电压尽量稳定。在这种情况下，需要为器件提供一种缓冲池，以便当外界环境剧烈变化时，器件的工作电压能保持相对的稳定。电容的本质是储存电荷和释放电荷，当外界环境变化时，电容中的电荷能被迅速积累或释放。根据公式  $\Delta U = \Delta Q/C$  ( $\Delta U$  表示电容两端电压的变化量， $\Delta Q$  表示电容两端电荷的变化量， $C$  为电容的容值)，当外部环境的变化驱使器件的工作电压增加或减少时，电容能通过积累或者释放电荷以吸收这种变化，即将器件工作电压的变化转变为电容中电荷的变化，从而保持器件工作电压的稳定。因此，电容的作用之一就是电荷缓冲池，以使高速运行器件的工作电压保持稳定。

#### 2) 电容的作用之二——高频噪声的重要泄放通路

对高速运行的电路而言，无时无刻不存在状态的转变。例如，信号的状态不断在 1 和 0 之间切换，器件的电流方向不断在输出和输入之间切换。这种高速的转变，将在电路上产生大量的噪声等干扰。从频谱上看，这些干扰在相当大程度上处于有效信号的 2 次、3 次等倍频频率。在电源传输路径上，需要将这些干扰泄放到相对稳定的地平面上，以免影响器件的工作。根据公式  $Z=1/(j\omega C)$ ，当频率较高时，电容表现为低阻抗，因此，可将电容作为高频噪声的重要泄放通路。

#### 3) 电容的作用之三——实现交流耦合

当两个器件通过高速信号互连时，信号两端的器件可能对直流分量有不同的要求。例如，A 和 B 两个器件之间通过高速差分对信号互连，但 A 器件工作于 1.8V，B 器件工作于 3.3V，则 A 器件驱动的差分对信号将携带 1.8V 直流分量，导致信号到达接收端 B 器件时无法被正确识别；反之，B 器件驱动的信号，到达 A 器件，其电平可能超过 A 器件所允许的最大输入电平。对于这种情况，需要将信号所携带的发送端的直流分量在达到接收端前，予以滤除，即隔离信号两边器件的直流分量。基于电容的通交流、阻直流的天然特性，电容具有这种隔离功能。因此，电容的作用之三是实现交流耦合 (AC Couple)，以实现对直流的隔离 (DC Blocking)。

## 2. 电容等效电路的分析

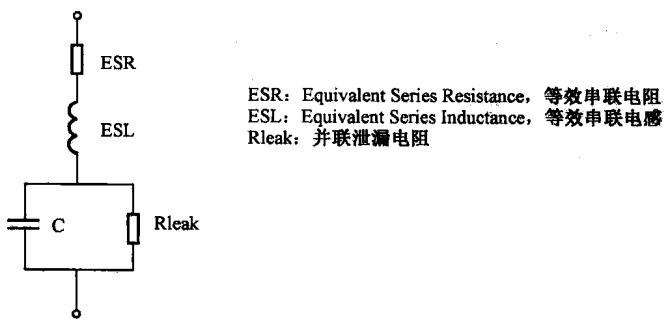

如图 2.8 所示，在高速设计领域，电容器件并不是纯粹的电容，而是带有电阻、电感等成分的小电路。其中 ESL 由电容器件的引脚电感和电容器件两极间等效电感串联而成，主要取决于封装；ESR 由电容器件的引脚电阻和电容器件两极间等效电阻构成，主要取决于电容工作温度、工作频率以及电容体本身的导线电阻等；Rleak 则取决于电容器件本身特有的泄漏特性。可以认为，电容器件的特性同时取决于电容分量、ESL 分量、ESR 分量及泄漏特性。

### 1) 电容分量

以一个案例来分析电容器件的电容分量对高速设计的影响。

### 【案例 2.7】 交流耦合电容选择不当引起数据帧出错

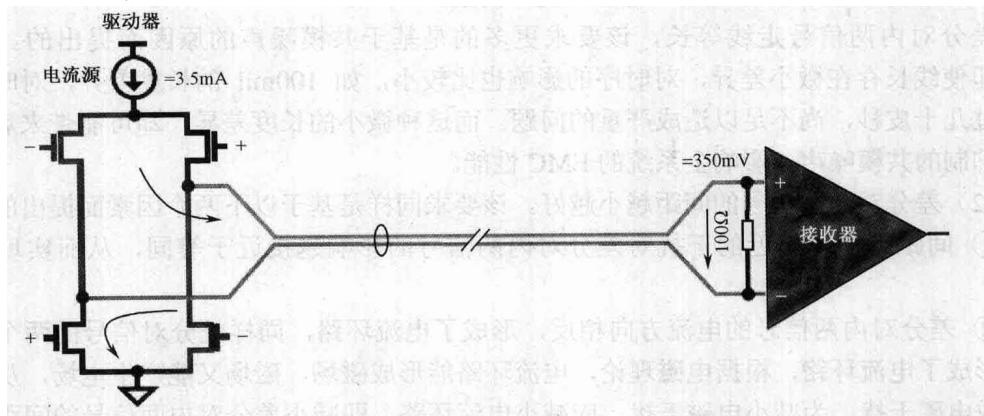

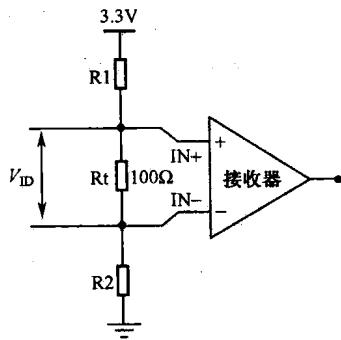

如图 2.9 所示, 某产品主控板和业务板的 FPGA 通过背板上电平为 LVPECL 的差分对信号线互连, 数据速率是 800Mbps (Mbps: 兆比特位每秒), 为隔离两板间直流偏置电平的相互影响, 采用交流耦合, 耦合电容选用 0.01μF 的陶瓷电容。测试发现, 发送某些码型时, 接收方经常检测到数据帧出错。

图 2.9 交流耦合电容选择不当引起数据帧出错

### 【讨论】

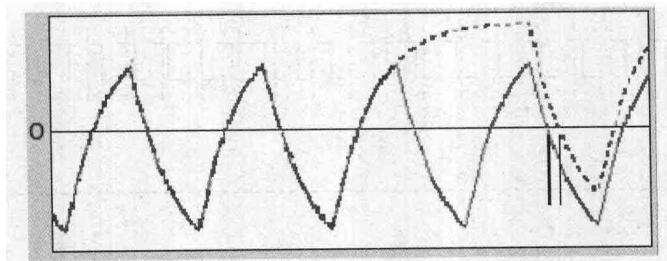

仔细研究出错的码型, 发现它们都有一个共同的特性, 即存在较长连续 0 和连续 1 比特位的情况。从逻辑设计工程师处获知, FPGA 并没有对发送的数据帧进行扰码处理, 而是将原始数据帧直接发送到外部信号线上。交流耦合电容在正常工作时, 处于平衡的充放电状态, 但原始数据帧中较长连 0 和连 1 比特位的出现, 打破了这种平衡, 使得信号通过判决门限的时间发生抖动, 导致接收端判决出错。

在交流耦合中, 电容串接在线路中, 阻抗为  $1/j\omega C$ 。容值越小的电容, 对低频信号所表现出的阻抗越大, 使低频信号的衰减越严重。

定义  $T_c$  为每比特位的数据周期, NUM 为最大容许连 0 或连 1 比特位的数目, 负载的阻抗为  $R$  (一般取  $50\Omega$ ),  $C$  为交流耦合电容容值。则有经验公式:

$$C_{\min} = 7.8 \times \text{NUM} \times T_c / R \quad (2.2)$$

本例中,  $T_c=1.25\text{ns}$ ,  $R=50\Omega$ , 根据码型分析, 本产品应用中可能出现的最大连 0 或连 1 比特位的长度为 85, 因此设定  $\text{NUM}=86$ , 则交流耦合电容的最小取值要求为

$$C_{\min}=7.8 \times 86 \times 1.25\text{ns} / 50\Omega = 16.77\text{nF} = 0.01677\mu\text{F}$$

设计中, 选用  $0.01\mu\text{F}$  的耦合电容, 显然无法满足式 (2.2), 导致数据帧出错。

在设计时需注意, 耦合电容取值也不能太大, 如果容值太大, 将无法满足高速信号变换的边沿斜率要求。在高速设计中, 一般取耦合电容的容值为  $0.1\mu\text{F}$ , 这样既可以满足数据帧中可能出现的长 1 长 0 情况, 又能满足高速信号变换的要求。

## 2) ESL 分量

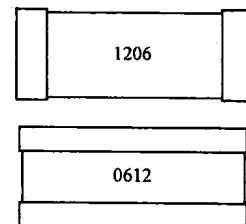

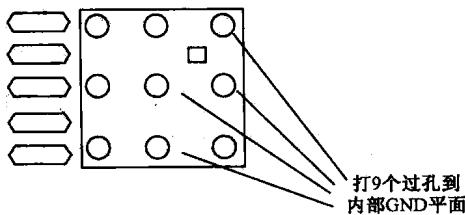

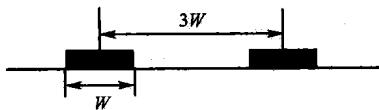

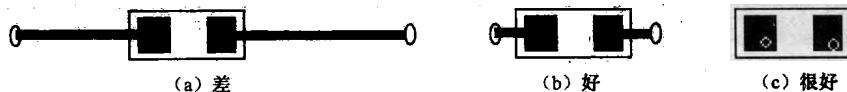

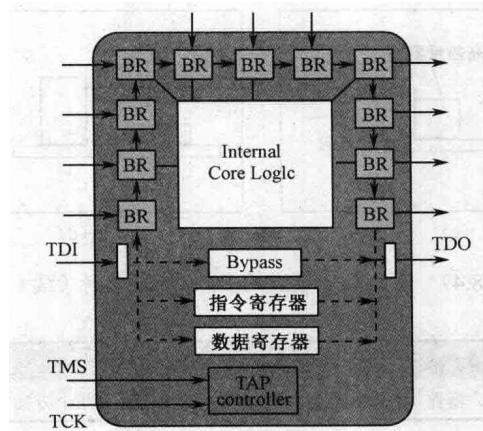

如何利用封装信息获得大致的 ESL 值? ESL 值取决于电容器件的类型和封装。在高速电路中, 应选用 ESL 值小的贴片电容, 因此仅以小尺寸贴片式的陶瓷电容作为示例, 对于插孔式电容, 如铝电解电容, 其 ESL 值将比表 2.2 所列出的值大得多。从表 2.2 知, 随着封装的增大, ESL 值将随之增大。比较特殊的是 0612 封装的贴片电容, 其 ESL 值不仅远远小于相同外形尺寸的 1206 的 ESL 值, 甚至小于目前业界尺寸最小的 0201 封装的 ESL 值。如图 2.10 所示为 1206 和 0612 封装的电容。

图 2.10 1206 和 0612 封装的电容

表 2.2 ESL 和封装对应关系<sup>[2]</sup>

| 封装尺寸     | 0201 | 0402 | 0603 | 0805 | 1206 | 0612 |

|----------|------|------|------|------|------|------|

| ESL (pH) | 400  | 550  | 700  | 800  | 1250 | 63   |

0612 封装的电容, 其长边为焊接边, 连接 PCB 上的焊盘, 相比 1206 封装, 一方面可以有更大的、能直接和 PCB 焊盘贴合的面积; 另一方面, 其内部电容体到 PCB 焊盘的距离也更近, 因此 ESL 值最小。就成本而言, 在相同容值的条件下, 0612 封装比 1206 封装只是略微贵一些。

## 【案例 2-8】 利用 0612 封装的电容增强滤波性能

结合案例 2-6, 更正后的 VCC\_PLL 滤波电路如图 2.11 所示。

图 2.11 利用 0612 封装的电容增强滤波功能

## 【讨论】

对 VCC\_PLL 的滤波，使用了两个 0612 封装的滤波电容。一个就近 CPU 的 VCC\_PLL 引脚放置，一个布放在 VCC\_PLL 这条信号线（PCB 上应加粗）离 CPU 引脚最远的位置。第一个电容的作用是滤除外界对 CPU 引脚的干扰，第二个电容的作用是消除 CPU 引脚对外界的影响。

### 3) ESR 分量、泄漏特性及其他信息

以下讨论如何通过阅读电容的器件资料来获得信息。

表 2.3 为截取自某电容的器件资料。

表 2.3 电容元件资料<sup>[11]</sup>

| Size Code<br>(尺寸编<br>号) | Part Number<br>(器件料号) | Rated<br>Voltage<br>(额定电<br>压) (V) | Rated<br>Capacitance<br>(额定电容)<br>( $\mu$ F) | ESR (内部串行电<br>阻) 100~300kHz<br>(m $\Omega$ )(max.) | Rated Ripple<br>Current (额定<br>纹波电流)<br>100kHz<br>(mAms)at106°C | Tangent of loss<br>angle (电容<br>损耗角正切<br>值) (max.) | Leakage<br>Current( $\mu$ A)<br>(泄漏电流)<br>(max.) $\times 1$ |

|-------------------------|-----------------------|------------------------------------|----------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------|

| C6                      | 16SEPC100M            | 16                                 | 100                                          | 24                                                 | 2400                                                            | 0.10                                               | 320                                                         |

| C9                      | 16SEPC100MW           | 16                                 | 100                                          | 10                                                 | 4500                                                            | 0.10                                               | 500                                                         |

|                         | 2SEPC560MW            | 2.5                                | 560                                          | 7                                                  | 5600                                                            | 0.10                                               | 500                                                         |

Size Code：厂家制定的尺寸编号。

Part Number：厂家制定的器件料号，采购时需要向厂家提供该参数。

Rated Voltage：额定电压，器件最高工作电压不能超过该值。

ESR：在 100~300kHz 频带范围内，电容器内部串行电阻的最大值，该值随着工作频率而变化，因此需要根据实际应用的频带范围取值。如果应用的频带范围不在厂家提供的参数表中，需要向厂家咨询。

Rated Ripple Current：本例中的电容一般用在单板的总电源处，因此需要能承受上下电时大电流的冲击，此参数的值越大，表示承受大电流冲击的能力越好。

Tangent of loss angle：电容损耗角正切值。理想电容工作时，产生无功功率  $Q$ （无损耗），由于电容内部存在 ESR 及泄漏电流，实际应用中会产生一定的损耗功率  $P$ ，定义  $\tan \delta = P/Q$ ， $\tan \delta$  就称为电容损耗角正切值。这个值越小，电容的功率损耗就越小。

Leakage Current：电容内部存在 Rleak（见图 2.8），因此存在泄漏通路，该参数用于定义流过电容的泄漏电流。

## 【案例 2.9】 LDO 电源应用中的滤波电容 ESR 问题

某单板上 FPGA 供电选用 Linear 公司 LDO 电源芯片 LT1963，输出电压 1.5V。LT1963 的外部滤波电容选取 10 $\mu$ F，尺寸为 0805、类型为 X5R 的陶瓷电容。在单板的调试中发现，上电时，在 LDO 输出的 1.5V 电源上会出现一个瞬间高达 1.8V 的冲击。最初设计者认为是外部电容容量不够所致，增加一个相同的 10 $\mu$ F 陶瓷电容，现象依旧。仔细阅读 LDO 芯片资料，发现资料提到，该 LDO 需要利用外部电容的 ESR 作为高频补偿，ESR 太小的电

容不足以满足这个要求。资料要求外部电容的 ESR 不能超过  $3\Omega$ ，同时要求在电容值为  $10\mu F$  时，电容的 ESR 不可小于  $20m\Omega$ 。设计中使用的  $10\mu F$  陶瓷电容，其 ESR 在工作频段内仅为  $6m\Omega$ ，无法满足要求。将该电容替换为  $10\mu F$  的钽电容，其 ESR 在  $100kHz$  时为  $2\Omega$ 。替换后， $1.5V$  电源上电正常。

### 【讨论】

提到电容的 ESR，设计者往往想到的都是其负面影响。的确，较大的 ESR 有两个不利因素。第一，根据电容损耗角正切值的定义，较大的 ESR 会产生较大的损耗功率  $P$ ，如果  $P$  大到一定程度，且单板上该类型的电容器件数目较多时，功耗预算就不得不考虑电容上的损耗，这往往是电子设计工程师最不希望看到的。第二，对于高速电路设计，往往希望电容的阻抗越小越好。这有两个含义，一方面，对于高频信号的交流耦合，电容串联在高频信号上，目的是隔断高频信号收发两端的直流分量，同时又希望高频信号的衰减越小越好，如果电容的 ESR 较大，对于交流耦合的高频信号，相当于在信号中间串联了一个不小的电阻，将产生一定的衰减；另一方面，对于并联在电源和地之间的滤波电容，其作用是为噪声等干扰信号提供一个极低阻抗的回路，ESR 较大的电容，显然无法起到这个作用。对于高速电路，即使 ESR 很小的电容，其 ESR 值仍不能满足低阻抗要求，因此，在重要的电源滤波电路上，往往需要并联多个电容，以最大程度地降低 ESR。

不过情况也有例外，本例中电容的 ESR 就被用于 LDO 芯片的高频补偿。其原理在于，当 LDO 电源的负载电流发生瞬时变化时，利用 ESR 能立即产生电压波动，从而引起 LDO 电源反馈电路的动作，以便 LDO 电源针对负载变化做出快速的调整。

#### 理解要点：

- ① 电容器件并不是纯粹的电容，而是带有 ESR、ESL、R<sub>leak</sub> 等分量的小型电路。

- ② ESL 取决于电容器件的类型和封装，ESR 取决于工作温度、频率、导线电阻等。

- ③ 大多数情况下，电容器件的 ESR 越小，电路性能越好，但也有例外，设计时需要根据器件的要求进行选型。

### 3. 滤波电容阻抗随频率变化特性的分析

高速电路设计需要考虑高频和低频两种噪声，针对这两种噪声，应选取不同的滤波电容。“低频噪声选用大电容，高频噪声选用小电容”，这是许多工程师达成的共识。在实际工作中，这种说法并不完全正确。我们将就这点进行一些探讨，以便加深对电容选型的理解。

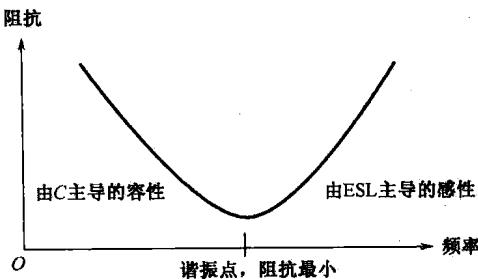

对电容器件而言，由于电容分量的存在，电容器件的阻抗随着频率的升高而逐渐降低，这是电容器件的本体属性；ESL 分量则使阻抗随着频率的升高而逐渐增加。这两种作用正好相反。在电容分量和 ESL 分量的共同作用下，电容器件的整体阻抗表现为，随着频率的升高，首先是电容分量起主导作用，使阻抗逐步变小，器件表现为电容的阻抗特性，滤波效果渐强；当达到某一频点时发生谐振，此时电容分量和 ESL 分量对阻抗的效果正好抵消，在谐振点上，电容器件阻抗最小，等于 ESR 分量；此后，随着频率继续升高，ESL 分量起主导作用，使阻抗逐步增大，器件表现为电感的阻抗特性，滤波效果渐弱。

滤波电容的作用机制是为噪声等干扰提供一条低阻抗回路，在噪声频率点上，要求滤波电容的阻抗较小，即当噪声频率落在谐振点附近时，滤波效果最好。如图 2.12 所示，谐振点由两条曲线交会而成，左边的曲线取决于电容器件的容值  $C$ ，右边的曲线取决于电容器件的 ESL。由谐振频率公式： $F = (ESL \times C)^{-1/2}$  知， $C$  和 ESL 越大，则谐振频率越低，即电容对高频干扰的滤波效果越差； $C$  和 ESL 越小，谐振频率越高，越适于滤除高频干扰。

图 2.12 电容器件的阻抗—频率变化曲线

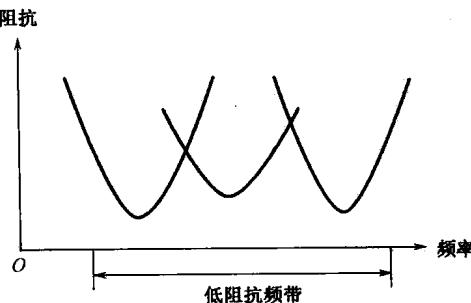

高速设计中，噪声等干扰往往不是处在一个频率点上，而是占据一段频带。在实际工作中，期望电路上每一处的噪声频带都得到准确定位并不现实，这就要求设计者在电路设计中，利用多种不同的电容构造一个比较宽的低阻抗频带，以尽可能地覆盖噪声频带。

如图 2.13 所示，用三种电容并联，其效果是构成一段比较宽的低阻抗频带。

图 2.13 多种电容器件构成低阻抗频带

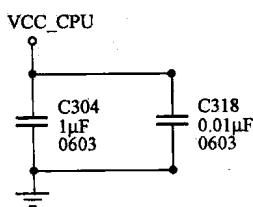

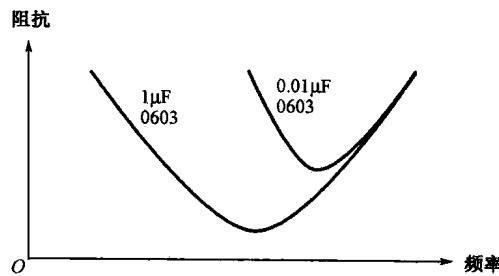

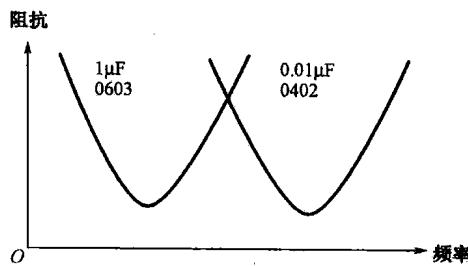

### 【案例 2-10】 高频电路中 $1\mu F + 0.01\mu F$ 是否能展宽低阻抗频带

图 2.14  $1\mu F$  和  $0.01\mu F$  并联滤波

某单板使用 0603 封装的  $1\mu F$  和  $0.01\mu F$  陶瓷电容各一个（见图 2.14），为 CPU 片内锁相环的电源滤波，设计者本意是利用两种不同的电容达到展宽低阻抗频带的效果，但是这样的设计是否能达到目的呢？

#### 【讨论】

电容器件的阻抗—频率曲线由其电容分量和 ESL 分量共同决定，本例中的两个电容容值不同，但类型和封装都相同，因此 ESL 相同，并联后的阻抗—频率曲线如图 2.15 所示，不能达到展宽低阻抗频带的目的。

图 2.15 0603 封装的  $1\mu\text{F}$  和  $0.01\mu\text{F}$  电容并联后的阻抗—频率曲线<sup>[61]</sup>

针对本例，改进方法是，仍旧选择  $1\mu\text{F}$  和  $0.01\mu\text{F}$  的陶瓷电容，不过封装分别选取 0603 和 0402，并联后的阻抗—频率曲线如图 2.16 所示。

图 2.16 0603 封装的  $1\mu\text{F}$  和 0402 封装的  $0.01\mu\text{F}$  并联后的阻抗—频率曲线<sup>[61]</sup>

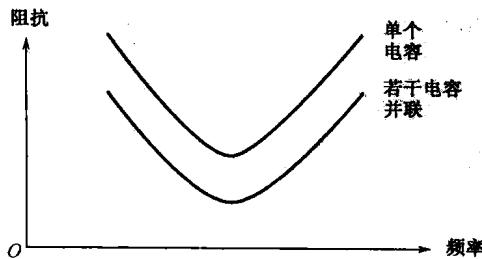

此处需做一些补充，设计者们常喜欢把若干相同的电容并联在一起，共同为某一电源滤波。这样做的目的，一方面是起到去耦电容的本地“小池塘”作用（参见 2.2.4 节），另一方面是为了在谐振点上得到更低的阻抗。需要说明的是，这样做，并没有展宽低阻抗频带。其阻抗—频率曲线如图 2.17 所示。

图 2.17 同型号电容并联后阻抗—频率特性曲线

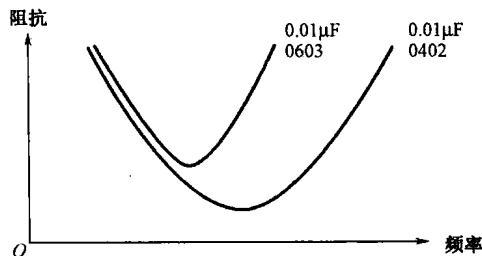

下面来分析“低频噪声选用大电容，高频噪声选用小电容”这种说法。结合电容器件的阻抗—频率曲线图，如果仅考虑电容器件的电容分量，这种说法是正确的，因为电容分量越大，谐振点的频率越低，适于滤除低频噪声，而电容分量越小，谐振点的频率越高，适于滤除高频噪声。但如果同时考虑 ESL 分量，则未必正确，参见图 2.15，0603 封装的  $0.01\mu\text{F}$  电容，其阻抗—频率曲线完全被 0603 封装的  $1\mu\text{F}$  电容的曲线包含，并没有真正起到作用。

需要补充的是，当两种电容器件的类型与容值相同，只有封装不同时，各自的阻抗—频率曲线将如何表现？以 0603 和 0402 的  $0.01\mu\text{F}$  陶瓷电容为例，其阻抗—频率曲线如图 2.18 所示，显然 0402 封装的阻抗—频率曲线能包含 0603 封装的曲线，如果设计中将这两种电容并联后为同一电源滤波，除了降低滤波电路的阻抗外，0603 封装的电容其实没有

真正发挥作用。

图 2.18 0603 封装  $0.01\mu\text{F}$  和 0402 封装  $0.01\mu\text{F}$  的阻抗—频率曲线

**理解要点：**

- ① 电容器件的阻抗—频率变化曲线是一种浴盆曲线，曲线的左边取决于电容分量，右边取决于 ESL 分量。

- ② 滤波电容并联以展宽低阻抗频带时，不仅要考虑容值搭配，还需要考虑封装搭配。多个同型号的电容并联时，虽不能展宽低阻抗频带，但可以减小谐振点处的阻抗。

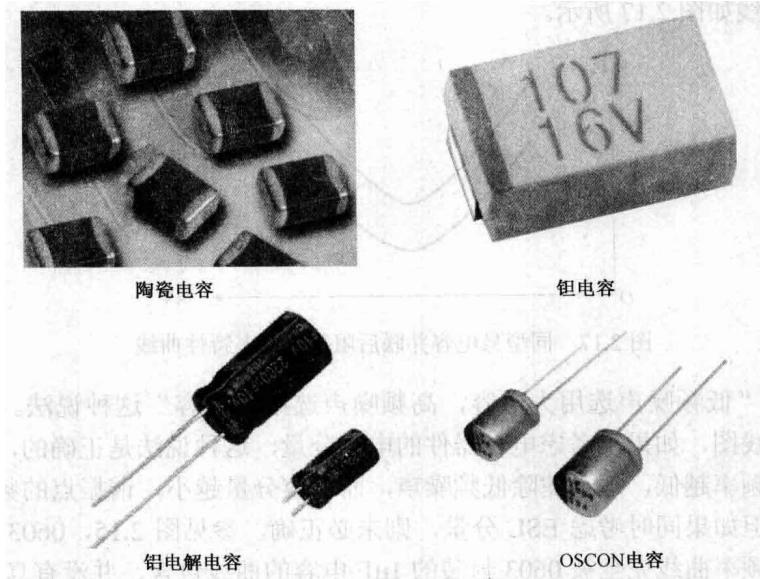

### 2.2.3 高速电路设计常用电容及其应用要点

高速电路设计中最常用的电容有陶瓷电容（Ceramic Capacitor）、钽电容（Tantalum Capacitor）、铝电解电容（Aluminum Electrolytic Capacitor），以及最近开始流行的 OSCON 电容，如图 2.19 所示。四种常用电容中，只有陶瓷电容是非极性电容，其他三种都属于极性电容。

图 2.19 认识各种电容

#### 1. 陶瓷电容及其应用要点

陶瓷电容是以陶瓷作为介质，在陶瓷的两面喷涂金属作为极板构成的，其优势是体积

小、价格低、稳定性好，但容量小。目前常用的陶瓷电容，其容值小的可以到几十皮法，大的可以到几十微法。

平时经常提到的 X7R、X5R、Y5V 等，就是陶瓷电容。那么这些符号的含义是什么？如表 2.4 所示为陶瓷电容的符号表示法。

表 2.4 陶瓷电容的符号表示法

| 第一个字母 | 最低温度  | 中间的数字 | 最高温度   | 最后一个字母 | 温度稳定性 $\Delta C/\Delta T$ |

|-------|-------|-------|--------|--------|---------------------------|

| Z     | +10°C | 2     | +45°C  | A      | +/- 1.0%                  |

| Y     | -30°C | 4     | +65°C  | B      | +/- 1.5%                  |

| X     | -55°C | 5     | +85°C  | C      | +/- 2.2%                  |

|       |       | 6     | +105°C | D      | +/- 3.3%                  |

|       |       | 7     | +125°C | E      | +/- 4.7%                  |

|       |       |       |        | F      | +/- 7.5%                  |

|       |       |       |        | P      | +/- 10.0%                 |

|       |       |       |        | R      | +/- 15.0%                 |

|       |       |       |        | S      | +/- 22.0%                 |

|       |       |       |        | V      | +22.0%~-82.0%             |

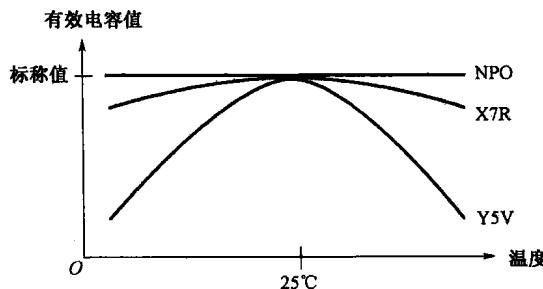

高速电路设计中，常用到的陶瓷电容种类有 NPO、X7R、X5R 和 Y5V。它们的区别主要在于填充介质不同，从而引起温度、电压稳定性的不同。

NPO 是温度补偿型陶瓷电容，是电容量最稳定的一种陶瓷电容。工作温度范围为  $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$ ，可以认为在这个范围内，电容量基本保持不变。

X7R，表示工作温度范围为  $-55^{\circ}\text{C} \sim +125^{\circ}\text{C}$ ，温度稳定性为  $+/- 15\%$  的陶瓷电容。

X5R，表示工作温度范围为  $-55^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ，温度稳定性为  $+/- 15\%$  的陶瓷电容。

Y5V，表示工作温度范围为  $-30^{\circ}\text{C} \sim +85^{\circ}\text{C}$ ，温度稳定性为  $+22\% \sim -82\%$  的陶瓷电容。

在高频电路设计中，推荐选用 NPO、X7R、X5R 类型，尽量不选用 Y5V 类型。

### 【案例 2-11】 陶瓷电容选型错误导致单板丢数据包

某成熟的低端以太网交换机产品在进行降成本设计后，高温  $55^{\circ}\text{C}$  下测试丢包率时发现丢数据包。该问题只发生在降成本设计后的批次上，之前的产品批次均能正常工作。查询改板记录，发现设计人员为了节省成本，将单板上为交换芯片供电的电源的  $10\mu\text{F}$  滤波电容的类型由 X7R 更改为 Y5V，电容厂家是 AVX。根据厂家提供的软件 SpiCap，可以计算出在  $85^{\circ}\text{C}$  时，电容容量仅为  $3.775\mu\text{F}$ ，尚不到标称电容值的 40%。而在环境温度  $55^{\circ}\text{C}$  时，单板上该电容附近的温度达到了近  $80^{\circ}\text{C}$ ，因此实际有效电容值相对标称值大为减小，无法满足滤波的要求，造成电源上噪声过大。将电容类型更改为同容值的 X7R 后，问题得到解决。

### 【讨论】

对于 X7R、X5R 和 Y5V 这三种类型的陶瓷电容，标称的电容值都是在环境温度  $25^{\circ}\text{C}$ 、工作电压等于  $0\text{V}$  时得到的值。如果环境温度和工作电压发生改变，则有效电容值将会发生变化。三者的区别在于变化程度的不同，其中 Y5V 这种类型的电容，变化最为剧烈。

利用 AVX 公司的 SpiCap 软件分析额定电压  $10\text{V}$ 、标称值  $22\mu\text{F}$  的 Y5V 电容，理想状

态（即工作电压 0V，环境温度 25°C）下，有效值为标称值（22μF）。如果保持其环境温度为 25°C 不变，仅改变工作电压，当工作电压为 5V 时，有效电容值为 4.4μF；当工作电压达到额定电压 10V 时，有效电容值仅为 2.2μF。如果保持其工作电压为理想的 0V 不变，仅改变环境温度，可以发现当环境温度相对于 25°C 升高和降低时，有效电容值都会减小，当环境温度达到 85°C 时，有效电容值为 8.30μF，为 -30°C 时，有效电容值为 8.36μF。

同样利用 SpiCap 软件分析 X7R 类型陶瓷电容（X5R 类型陶瓷电容的分析结果和 X7R 类似），可以发现设定工作电压为理想的 0V 不变，环境温度达到极限的 -55°C 和 125°C 时，有效电容值降到标称值的 85% 左右。而假定环境温度为理想温度 25°C 不变，工作电压达到额定电压时，有效电容值降到标称值的 75%。

我们知道，单板工作时，电容的工作电压不可能是 0V，附近的环境温度也不可能保持在 25°C，因此对电容必须进行降额设计，对 X7R 和 X5R 应至少降额 20% 使用，而 Y5V 则不建议在高速电路和环境温度变化剧烈的情况下使用。

图 2.20 所示为不同类型电容的容值随温度变化的曲线示意图，希望通过图 2.20，让大家深刻地理解电容降额的必要性。

图 2.20 陶瓷电容温度稳定性示意图

贴片式陶瓷电容的 ESR 值一般都比较小，在高频滤波中这是一个优势，但有些时候，这也是一个劣势，请参考案例 2-9。

由于陶瓷电容容量一般都比较小，在电源电路的设计中，单独使用陶瓷电容滤波是不适宜的，必须同时搭配使用钽电容、铝电解电容或者 OSCON 等类型的电容。

## 2. 钽电容及其应用要点

钽电容使用金属钽作为介质，基于钽的固态特质，具有温度特性好、ESL 值小、高频滤波性能好、体积小、节省 PCB 面积、容值较大等特点。因此钽电容一般被应用在需要大容量电容滤波的场合，如为 CPU 等高耗能器件滤波。

钽电容的缺点是耐电压和耐电流的能力较弱。一般要求钽电容的工作电压相对额定电压降额 50% 以上。遇到以下三种场合之一，钽电容的额定电压需降额 70% 以上使用：

- (1) 负载呈现较强的感性；

- (2) 串联电阻小；

- (3) 瞬变电流较大。

其原因在于，感性负载或较小的串联电阻会导致较大的瞬变电流，造成钽电容的金属钽介质被击穿。这使得在以下环节，钽电容的失效概率增大：ICT 测试、老化测试、系统开机瞬间、单板热插拔瞬间。

案例 2-5 中，在热插拔子板的过程中，会产生较大的瞬变电流，而连接器附近为子板电源滤波的钽电容电压降额只有 25%，没有达到 70% 的要求，因此造成失效。

一般而言，容值越大的钽电容，其 ESR 值往往越小。

图 2.21 是摘取自 AVX 公司的钽电容器件资料。10μF 的钽电容，其 100kHz 时的 ESR 最大值为 1500mΩ；150μF 的同系列钽电容，ESR 最大值仅为 125mΩ。

| AVX<br>Part No.<br>(产品型号)  | Case<br>Size<br>(封装<br>尺寸) | Capacitance(μF)<br>(容量) | Rated Voltage<br>(Voltage Code)<br>(额定电压) | DCL(μA)<br>Max.<br>(最大漏<br>电流) | DF(%) Max.<br>(最大容<br>量变化率) | ESR Max.(mΩ)<br>@100kHz<br>(最大等效<br>串联电阻) | 100kHz Ripple Current (mA) Ratings<br>(纹波电流) |       |                                    |

|----------------------------|----------------------------|-------------------------|-------------------------------------------|--------------------------------|-----------------------------|-------------------------------------------|----------------------------------------------|-------|------------------------------------|

|                            |                            |                         |                                           |                                |                             |                                           | 25°C                                         | 85°C  | 125°C                              |

| <b>Voltage/Code (额定电压)</b> |                            |                         |                                           |                                |                             |                                           |                                              |       | 6.3volt @ 85°C(4 volt @ 125°C) / J |

| TPSA685*006#1800           | A                          | 6.8                     | 6.3                                       | 0.5                            | 6                           | 1800                                      | 0.204                                        | 0.184 | 0.082                              |

| TPSA106*006#1500           | A                          | 10                      | 6.3                                       | 0.6                            | 6                           | 1500                                      | 0.224                                        | 0.200 | 0.089                              |

| TPSA156*006#1500           | A                          | 15                      | 6.3                                       | 0.9                            | 6                           | 1500                                      | 0.224                                        | 0.200 | 0.089                              |

| TPSA226*006#0900           | A                          | 22                      | 6.3                                       | 1.4                            | 6                           | 900                                       | 0.289                                        | 0.260 | 0.115                              |

| TPSB226*006#0600           | B                          | 22                      | 6.3                                       | 1.4                            | 6                           | 600                                       | 0.376                                        | 0.339 | 0.151                              |

| TPSA336*006#0600           | A                          | 33                      | 6.3                                       | 2.1                            | 6                           | 600                                       | 0.353                                        | 0.318 | 0.141                              |

| TPSB336*006#0600           | B                          | 33                      | 6.3                                       | 2.1                            | 6                           | 600                                       | 0.376                                        | 0.337 | 0.151                              |

| TPSW336*006#0400           | W                          | 33                      | 6.3                                       | 2.1                            | 6                           | 400                                       | 0.474                                        | 0.427 | 0.190                              |

| TPSB476*006#0500           | B                          | 47                      | 6.3                                       | 3.0                            | 6                           | 500                                       | 0.412                                        | 0.371 | 0.165                              |

| TPSC476*006#0300           | C                          | 47                      | 6.3                                       | 3.0                            | 6                           | 300                                       | 0.606                                        | 0.545 | 0.242                              |

| TPSB686*006#0500           | B                          | 68                      | 6.3                                       | 4.3                            | 6                           | 500                                       | 0.412                                        | 0.371 | 0.165                              |

| TPSC686*006#0200           | C                          | 68                      | 6.3                                       | 4.3                            | 6                           | 200                                       | 0.742                                        | 0.667 | 0.297                              |

| TPSC686*006#0150           | C                          | 68                      | 6.3                                       | 4.3                            | 6                           | 150                                       | 0.856                                        | 0.766 | 0.343                              |

| TPSW686*006#0250           | W                          | 68                      | 6.3                                       | 4.3                            | 6                           | 250                                       | 0.600                                        | 0.540 | 0.240                              |

| TPSC107*006#0150           | C                          | 100                     | 6.3                                       | 6.3                            | 6                           | 150                                       | 0.856                                        | 0.766 | 0.343                              |

| TPSC157*006#0250           | C                          | 150                     | 6.3                                       | 9.5                            | 6                           | 250                                       | 0.663                                        | 0.597 | 0.265                              |

| TPSC157*006#0150           | C                          | 150                     | 6.3                                       | 9.5                            | 6                           | 150                                       | 0.856                                        | 0.771 | 0.343                              |

| TPSD157*006#0125           | D                          | 150                     | 6.3                                       | 9.5                            | 6                           | 125                                       | 1.095                                        | 0.980 | 0.438                              |

图 2.21 钽电容器件资料<sup>[3]</sup>

根据电容的等效电路，ESR 相当于电容器件的串联电阻，串联电阻越小越容易造成钽电容失效。因此在应用中需要注意，对于大容值的钽电容，更需要电压降额。从成本上来说，钽电容的价格正比于容值和额定电压的乘积，在使用大容值的钽电容时，还需要增加电压降额的比例，这势必造成成本的上升。因而在设计中，往往将若干小容值的钽电容并联以提供和大容值钽电容相同的容量，这样做，一方面有利于设计的可靠性，一方面也有利于成本的降低。

需要注意，工作在瞬变电流较大的场合，钽电容并不一定会发生永久失效。钽电容本身有较好的自愈能力，只要外界环境的影响在一定范围之内，钽电容都能自我恢复。有时在单板的调试中会发现，单板突然莫名其妙地掉电，过一会儿后重新上电又能正常工作，有可能就是因为钽电容暂时失效所致。因此，为了保证单板长期稳定的工作，必须严格执行钽电容的电压降额，同时在设计时需注意，在涉及热插拔的电源滤波电路上，尽量避免使用钽电容。

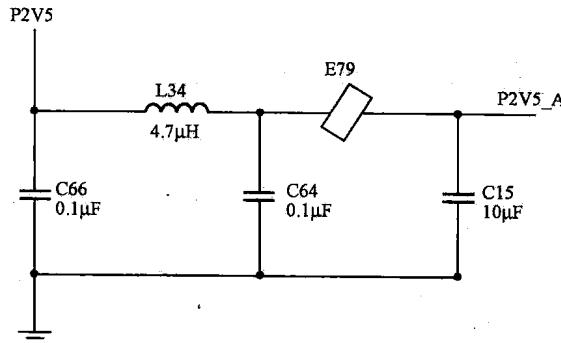

### 【案例 2-12】 根据电路要求进行钽电容选型

某 FPGA 的 I/O 接口电源为 1.8V，功耗 0.9W，要求电源电压的波动不超过 5%。电源完整性仿真表明，其主要噪声频段将集中在 100kHz~5MHz，根据以上需求选择滤波电容的型号。

#### 【讨论】

由于噪声频带集中在 100kHz~5MHz，可初步判断需要选择钽电容和陶瓷电容配合滤波，钽电容主要滤除低频段噪声，陶瓷电容滤除高频段噪声。

该 FPGA 的 I/O 接口电源，最大电流为  $0.9W/1.8V = 0.5A$ ，假定其电流波动值  $\Delta I$  不会超

过最大电流的 50%，即取  $\Delta I=0.25\text{A}$ 。

则该 I/O 接口电源的动态阻抗为  $Z=\Delta V/\Delta I=(1.8\text{V}\times 5\%)/0.25\text{A}=0.36\Omega$ 。

首先考虑低频段的滤波，选用钽电容，其 ESL 分量非常小，可以忽略，因此其阻抗主要由 ESR 和 C 构成，即  $Z_{\text{CAP}}=|\text{ESR}+1/j\omega C|=[(\text{ESR})^2+(1/\omega C)^2]^{1/2}$ 。

选择 AVX 公司的  $22\mu\text{F}$  电容 TPSB226#0600，根据图 2.21 所示器件资料，在  $100\text{kHz}$  时，其 ESR 最大值为  $0.6\Omega$ ， $Z_{\text{CAP}}=[0.36+1/(2\times 3.14\times 100\times 10^3\times 22\times 10^{-6})^2]^{0.5}=0.604\Omega$ 。

要求滤波电容的阻抗小于芯片动态阻抗，因此需两片  $22\mu\text{F}$  电容并联，并联后阻抗为  $0.302\Omega$ ，小于动态阻抗，所以可以满足低频段滤波的要求。

其次，对于高频段滤波，一般可以选用 0402 封装、X5R 类型、 $1\mu\text{F}$  的陶瓷电容。

结论，针对本例需求，设计上应采用 2 片  $22\mu\text{F}$  钽电容 TPSB226#0600，与若干  $1\mu\text{F}$  陶瓷电容并联（建议一个 I/O 接口电源引脚放置一个  $1\mu\text{F}$  陶瓷电容），为 FPGA 的 I/O 接口电源滤波。

高速电路中，噪声频段分布得比较广泛，设计时需要将陶瓷电容和钽电容配合起来共同完成滤波功能。

### 3. 铝电解电容及其应用要点

铝电解电容使用电解液作为介质，外壳的铝制圆筒作为负极，内部插入一块金属板作为正极。铝电容容量大、耐压高，但温度稳定性差、精度差、高频滤波性能差，仅适用于低频滤波。

在对钽电容的介绍中提到，钽电容不适用于有较大瞬变电流的场合，而在这种场合下，就需要用到铝电解电容。例如，在单板的  $-48\text{V}$  缓启电路上，就需要用到铝电解电容。

在应用中，铝电解电容的电压降额要求至少为 20%。例如，在  $-48\text{V}$  缓启电路的滤波电路中，要求铝电容的额定电压在  $60\text{V}$  以上。

铝电解电容一般都是插装式，因此 ESR、ESL 值都比较大，同时由于其采用液体作为介质，在极高温和极低温环境下，性能也极不稳定。

案例 2-4 的硬盘停止工作的问题，就是一个典型的铝电解电容在低温下性能不稳定的案例。查询铝电解电容器件资料如表 2.5 所示。

表 2.5 铝电解电容器件资料<sup>[4]</sup>

| 容量 ( $\mu\text{F}$ ) | 阻抗 $\Omega/100\text{kHz}$ |       | 纹波电流 mA<br>r.m.s./ $100\text{kHz}$ |

|----------------------|---------------------------|-------|------------------------------------|

|                      | 20°C                      | -10°C |                                    |

| 1.0                  | 2.40                      | 4.80  | 20                                 |

| 2.2                  | 1.80                      | 3.60  | 45                                 |

| 3.3                  | 1.30                      | 2.60  | 65                                 |

| 4.7                  | 1.30                      | 2.60  | 95                                 |

| 10                   | 1.30                      | 2.60  | 125                                |

| 12                   | 1.30                      | 2.60  | 135                                |

| 15                   | 1.30                      | 2.60  | 145                                |

| 18                   | 1.30                      | 2.60  | 155                                |

| 22                   | 1.30                      | 2.60  | 155                                |

表 2.5 中, 第二、三栏分别提供了该电容在 20℃ 和 -10℃ 的 ESR 值, 可以看出, 在 -10℃, 铝电解电容的 ESR 值相对常温增大了一倍, 而该案例的测试在 -30℃ 下进行, ESR 相比 -10℃ 时又会增大很多。即在 -30℃, 铝电解电容的 ESR 值比常温下的值可能大好几倍, 滤波性能大大降低。

从产品的长期稳定性来说, 铝电解电容也可能成为隐患。因为随着产品使用时间的增加, 铝电解电容内部的电解液将逐渐干涸, 容量逐渐减小, ESR 逐渐增大, 滤波效果减弱。

所以在高速电路设计的电容选型中, 应尽量避免选择铝电解电容。

#### 4. OSCON 电容及其应用要点

严格地说, OSCON 并不是一种电容的类型, 而是 SANYO 公司的一种性能比较好的电解电容的品牌。

OSCON 电容外形酷似铝电解电容, 其优点在于, OSCON 电容 ESR 较小、温度稳定性相对铝电解电容较好、价格相对钽电容较低。缺点在于对绝大多数 OSCON 电容而言, 引脚都是插装形式, 并且体积比较大。

在电路设计中, DC/DC 电源的输入和输出部分往往需要布放大容量的钽电容, 成本较高。在这种情况下, 可以同样容值的 OSCON 电容取代, 其成本仅为对应钽电容的几分之一。

#### 5. 总结

本小节就高速电路设计中的常用电容类型做了详细介绍, 各种电容均有自己的优势和劣势, 没有哪一种类型能够完全取代其他类型, 因此在设计中, 设计者们需要注意结合各种电容自身的特点, 配合使用, 以获得最佳效果。

##### 理解要点:

- ① 陶瓷电容体积小、价格低、稳定性好, 但容量小。适用于高频滤波。

- ② 钽电容温度稳定性好、ESL 值小、高频滤波性能好、体积小、能节省 PCB 面积、并且容值较大, 但耐冲击电压和冲击电流的能力较弱。

- ③ 铝电解电容容量大、耐压高, 但温度稳定性差、精度差、高频滤波性能差, 仅适用于低频滤波。

- ④ 在电容应用中, 应注意对阻抗一频率特性曲线的理解。

### 2.2.4 去耦电容和旁路电容

在技术资料上, 经常可以看到去耦 (decouple) 电容和旁路 (bypass) 电容这两种名称。它们都不是电容的类型, 而是设计者根据电容所起的作用不同而进行的人为划分。本小节不展开讲解这两种电容, 只简要介绍其作用。

去耦电容, 其作用是为保证器件稳定工作而给器件电源提供的本地“小池塘”。在高速运行的器件上, 会不断产生快速变化的电荷需求, 对于这种快速的需求, 电源模块无法及时给器件提供电流以补充, 只能依靠器件附近的电容给予解决。可以把电容理解成平时灌满水的小池塘, 一旦小池塘附近的庄稼缺水, 能立刻从小池塘得到补充, 而无需求助远方的水厂。去耦电容还有另一个作用, 是为高速运行器件产生的高频噪声提供一条就近流入地平面

的低阻抗路径，以避免这些干扰影响该电源的其他负载。

旁路电容，其作用是为前级（如电源产生的高频噪声等干扰）提供一条流到地平面的低阻抗路径，以避免这些干扰影响正在高速工作的器件。

从以上描述可以看出，去耦电容和旁路电容没有本质的区别，从应用上说，依据公式  $Z=1/(2\pi F \times C)$ ，其中  $F$  是器件工作频率，它们在高频下的作用都是为电路中的干扰提供一条流回地平面的低阻抗回路。

## 2.3 电感的选型及应用

### 2.3.1 与电感相关的经典案例

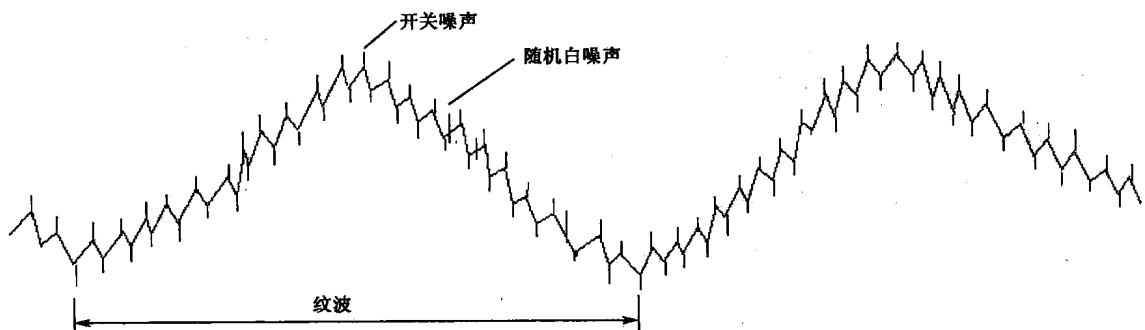

#### 【案例 2-13】 LC 低通滤波导致输出电源电压纹波偏大

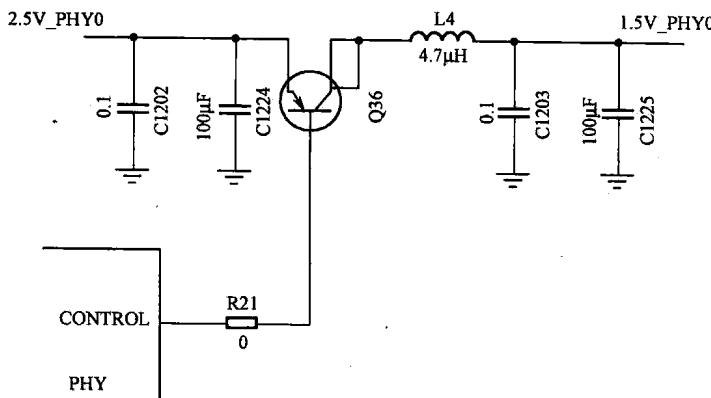

某 PHY 芯片的核心电压 1.5V，要求从本芯片的 I/O 接口电源 2.5V 产生。如图 2.22 所示，PHY 芯片通过 CONTROL 引脚控制外部 PNP 型管的通断，以产生 1.5V 电源。测试中发现，在 1.5V 电源上存在 160mV 纹波。

图 2.22 PHY 芯片电源的产生电路

#### 【讨论】

根据芯片厂家的信息，该芯片已应用在许多成功的设计上，从而可以排除 PHY 芯片本身故障的可能。与厂家确认，PHY 工作时，外部晶体管转换频率在 1~100MHz 频段内。

出于滤波的目的，本设计对 1.5V 输出电源采用了 LC 低通滤波器（L4 和 C1225），其谐振频率  $F=1/(2\pi\sqrt{LC}) = 1.59\text{MHz}$ ，处于 PNP 型晶体管工作频带内，因此可能产生谐振，分析可得出结论，该纹波应主要来自谐振时产生的剧烈振荡。

本设计中，LC 滤波器的本意是为滤除高频噪声，显然设计没有达到应有的效果。仔细分析芯片资料得知，该电路的原理是，PHY 芯片内部有一个 LDO 控制电路，该控制电路通过 CONTROL 引脚控制外部 PNP 型晶体管以得到 1.5V，内部控制电路和外部的 PNP 型晶体管共同构成了一个 LDO 电源，完全没有必要采用 LC 滤波器。改版设计中，将 L4 删除，使晶体管的集电极直接连接到 1.5V 输出，经测试，1.5V 上纹波仅 7mV。

### 【案例 2.14】 大电流通路 PI 型滤波造成电压衰减

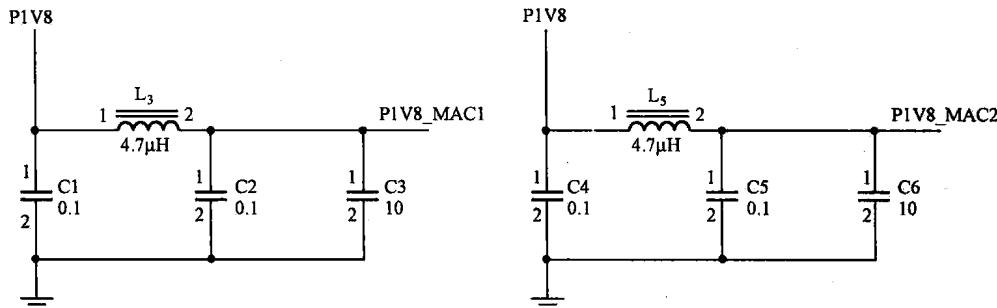

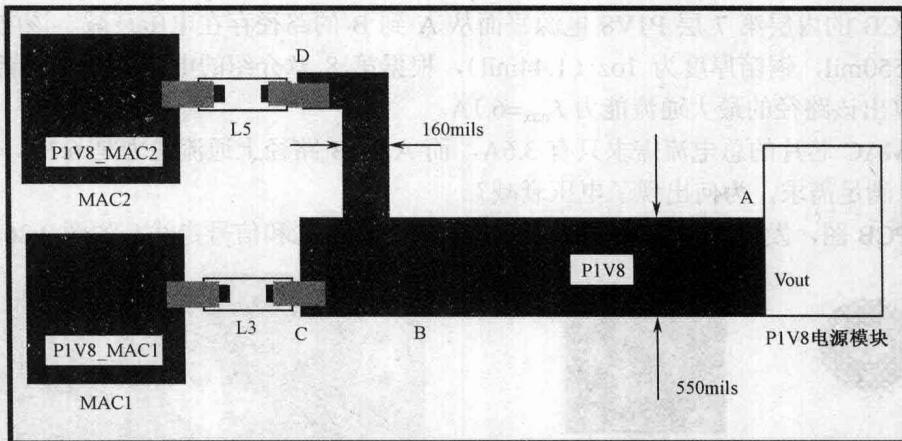

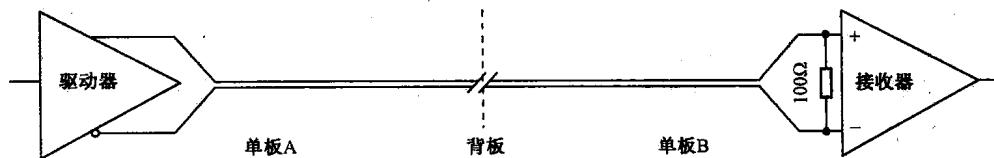

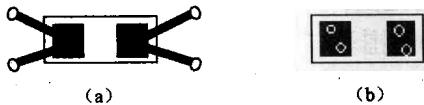

某单板的 1.8V 电源有三个 MAC 芯片（MAC 芯片：链路控制层芯片）作为负载，这些芯片主要分布于单板左侧靠近用户面板的 RJ45 接口侧。由于单板布局限制，1.8V 电源模块只能布放于单板右侧，利用 PCB 内层信号层（第 7 层），铺一个电源平面将 1.8V 传输到单板左侧。每个 MAC 芯片最大工作电流为 1.8A。由于 1.8V 电源平面的传输路径比较远，为滤除其在传输过程中可能受到的干扰，在 1.8V 上分别作 PI 型滤波后再送到各个 MAC 芯片，原理图如图 2.23 所示。

图 2.23 MAC 芯片 1.8V PI 型滤波电路

PCB 内层信号层的 1.8V 电源平面铺制如图 2.24 所示。

图 2.24 MAC 芯片 1.8V 电源平面分配

如图 2.24 所示，单板右侧的电源模块产生 1.8V（网络名为 P1V8），在信号层利用一个电源平面与 L3、L5 连接，经过 PI 型电路滤波后，产生 P1V8\_MAC1 和 P1V8\_MAC2，为 MAC 芯片供电。

经测试，P1V8\_MAC1 电压为 1.67V，P1V8\_MAC2 电压为 1.61V，不满足 MAC 芯片对 1.8V 电源的最小电压要求 1.62V。

#### 【讨论】

对于欠压问题，首先应考虑的是电源模块输出端。测量 P1V8 电源模块的输出端 A 点处电压， $V_A = 1.83V$ ，纹波电压 17mV，满足要求。

测量 P1V8 电源平面传输路径上的 B 点电压,  $V_B = 1.77V$ 。测量 P1V8 电源平面到达电感处的电压  $V_C = 1.77V$ ,  $V_D = 1.70V$ 。

可见, MAC 芯片处电源欠压的原因有两个: 第一, P1V8 电源平面上的电压衰减; 第二, 电感 L3 和 L5 造成的电压衰减。

首先, 分析 P1V8 电源平面上的电压衰减。检视 PCB 图, 发现以下潜在缺陷:

(1) 电源模块是插装式封装, 其输出引脚到第 7 层的 P1V8 电源平面的连接, 只用了一个过孔。电源模块输出的所有电流必须通过这个过孔才能到达第 7 层的电源平面, 因此该过孔实际上构成了电流传输路径上的一个关键点。

过孔通流能力的计算将在第 8 章介绍, 本设计中, 每片 MAC 全速工作时的电流要求为 1.8A, 所以总电流要求为 3.6A, 由通流能力计算可知, 该过孔无法满足 3.6A 的通流, 因此过孔成为瓶颈之一。

改进策略有两个。

① 策略 1: 采用花焊盘过孔代替普通过孔, 如图 2.25 所示。花焊盘过孔本身是为加强波峰焊时的散热而应用的一种孔, 在本例中, 则是利用了花焊盘过孔横截面积远远大于普通过孔横截面积的特点, 以增大其通流能力。

② 策略 2: 在表层电源模块输出引脚附近用一小块电源平面与输出引脚相连, 在电源平面上增加数个 P1V8 的过孔, 利用过孔与第 7 层的 P1V8 电源平面相连, 因此除了原有的花焊盘过孔作为主要通流路径外, 这些新增的过孔也增强了通流。在改板设计中, 同时采用了策略 1 和策略 2。

(2) PCB 的内层第 7 层 P1V8 电源平面从 A 到 B 的路径存在电压衰减。该电源平面路径宽度为 550mil, 铜箔厚度为 1oz (1.44mil), 根据第 8 章介绍的电源平面通流能力计算方法, 可计算出该路径的最大通流能力  $I_{max}=6.1A$ 。

两片 MAC 芯片的总电流需求只有 3.6A, 而 A 到 B 路径上通流能力是 6.1A, 即使降额 30% 也足以满足需求, 为何出现了电压衰减?

查阅 PCB 图, 发现在 A 到 B 路径上存在大量信号过孔和信号走线, 如图 2.26 所示。

图 2.25 普通常过孔和花焊盘过孔

图 2.26 路径上存在大量信号过孔和信号走线

图 2.26 截取自 PCB 设计图, 是 A 到 B 路径的一部分, 在左边有三个连续的过孔将该路径部分地阻断, 中间则有两条信号线引入电源平面, 将路径部分地阻断, 因此有效路径宽度远远小于 550mil, 在考虑过孔和信号线的因素后, 有效路径宽度仅 180mil, 根据第 8 章的相关公式, 可计算得到  $I_{max}$  为 2.75A, 无法满足 MAC 芯片的电流需求。

改版策略: 增加电源平面的路径宽度, 并将原来引入电源平面的信号线挪到其他信号层, 减少电源平面内的信号过孔, 将有效路径宽度增加到 510mil。

(3) B 到 D 的路径上有 0.07V 的压降, 该部分路径宽度为 160mil, 除去信号过孔的影响, 路径有效宽度仅 95mil, 根据公式,  $I_{max}=1.75A$ , 降额 30% 后, 最大通流能力仅 1.2A,

无法满足 MAC2 芯片的电流要求。

由于该路径上的信号过孔属于关键信号，且周围的高速信号非常多，因此信号过孔不能挪动，且路径宽度也无法增加。查看 PCB 其他层后发现，可以在第 15 层信号层增加一个 P1V8 的窄平面。

改板策略：在 B 和 D 处各增加 4 个 P1V8 过孔，以便将 P1V8 从第 7 层引到第 15 层，在第 15 层，利用窄平面将 B 和 D 连接。采用该策略后，虽然没有加宽第 7 层的原有电源平面路径宽度，但在其他层新增了一条路径，所以同样提高了通流能力。在这个过程中，同样需要考虑过孔的通流能力。

(4) 电感 L3 和 L5 上各有 0.1V 的压降。查看电感器件资料，额定电流为 2.7A，足以满足 MAC 芯片 1.8A 的需求。根据资料，该电感的最大直流电阻为  $0.088\Omega$ ，按照 MAC 的最大电流 1.8A 计算，其压降最大可能达到 0.16V。因此可以判断在电感上的压降主要来自电感的直流电阻。

改板时，选择另一个系列的低直流电阻的电感，以进一步降低电感的压降。

### 【结论】

这个案例是 PCB 电源平面设计的非常经典的案例。电源平面一旦出了问题，只能通过改板予以解决，势必造成研发周期的推迟。

在电源平面设计中，需要考虑的因素非常多。由本案例的讨论部分可见，对电源平面的设计，往往需要结合一些经验公式。但需要提醒设计者的是，经验公式的前提都是基于比较理想的情况，如电源平面本身不受干扰等，在实际应用中，不会出现理想的情况，因此对于经验公式得到的结果，必须做一定的降额。

本案例是一个比较综合的案例，虽然不是完全与电感相关，但实际应用中所遇到的电源路径上的压降问题，许多都根源于电感的压降。因此，在电感应用于电源滤波电路时，除考虑滤波性能外，设计者还应考虑电感本身的压降。

## 2.3.2 高速电路设计中电感的作用

### 1. 电感的作用之一——通直流、阻交流

在电容一节提到，电容的作用是通交流、阻直流。那么，是否存在需要通直流、阻交流的场合？以电源为例，DC/DC 直流电源是通过不断地开、合 MOSFET 管以形成所需的电源电压。开、合的过程含有大量的交流分量，而这些交流分量是直流电源所不需要的。根据公式  $Z=j\omega L$ ，频率越高，电感阻抗越大，反之，电感阻抗越小。因此电感天生具有通直流、阻交流的功能，即电感的作用之一是：通直流、阻交流。

### 2. 电感的作用之二——阻碍电流的变化，保持器件工作电流的稳定

电感是用外表绝缘的导线绕制而成的、电磁敏感的线圈。当线圈中通有电流时，线圈周围会产生磁场。当电流变化时，线圈感应出电动势，以产生与电流方向相反的感应电流，阻碍这种电流的变化。因此，电感的作用之二是，阻碍电流的变化，保持器件工作电流的稳定。

### 3. 电感的作用之三——滤波

电平状态高速变换的信号，往往寄生有大量的高频谐波，这些谐波是影响电路工作的

噪声。在电路设计中，需要构建低通滤波器滤除这些高频噪声。根据电路原理，低通滤波器往往基于电感和电容构建。因此，电感的作用之三是滤波。

### 2.3.3 高速电路设计常用电感及其应用要点

根据电感的应用场合，可将电感分为高频信号用电感、一般信号用电感和电源用电感<sup>[6]</sup>。从器件资料上，需要得到以下关键信息：

- 电感值

- 直流电阻

- 自谐振频率（ $Q$  最大时的频率）

- 额定电流

以下就不同类型电感进行具体分析。文中所列举的参数主要取自电感器件厂家 TDK 的相关资料。

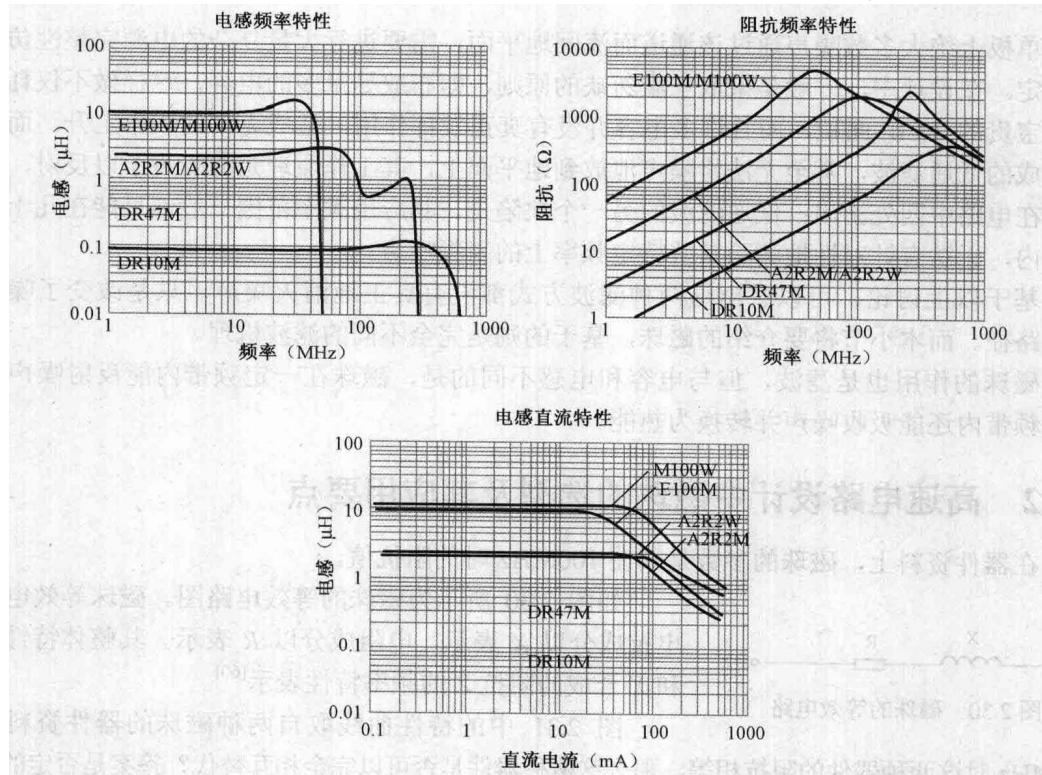

#### 1. 高频信号用电感

高频信号用电感主要用在射频信号上。

##### 1) 主要参数

- ① 电感值范围：0.6~390nH。

- ② 直流电阻：有多种直流电阻可供选择。一般而言，电感值越大，其对应的直流电阻也越大。

- ③ 自谐振频率：可以高达 12GHz。电感值越大，其对应的自谐振频率往往越小。

- ④ 额定电流：几十毫安到几百毫安。电感值越大，其对应的额定电流往往越小。

##### 2) 应用特点

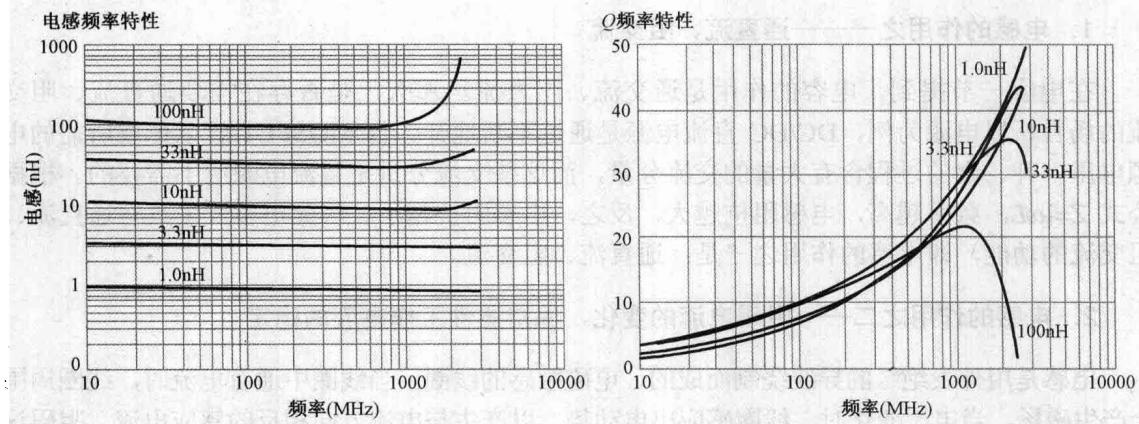

电感值和自谐振点与工作频率的关系如图 2.27 所示。

图 2.27 电感值和自谐振点与工作频率的关系<sup>[6]</sup>

从图 2.27 可知，工作频率小于谐振频率时，电感值基本保持稳定；但一旦工作频率超过谐振频率后，电感值将会迅速增大，不过，若频率继续增大并达到一定程度后，电感值又会迅速减小（减小的这个过程没有在图 2.27 中体现）。

在应用中，应选择谐振频率点高于工作频率的电感。

对于高频信号用电感而言，谐振频率点一般在 1GHz 以上，因此该类电感可支持很高的工作频率。

## 2. 一般信号用电感

一般信号用电感主要用在高速信号上。

### 1) 主要参数

- ① 电感值范围：0.01~1000 $\mu$ H。

- ② 直流电阻：有多种直流电阻可供选择，电感值越大，对应的直流电阻也越大。一般信号用电感，其直流电阻比高频信号用电感和电源用电感大一些，最小的直流电阻一般为 100m $\Omega$ ，大的可达到几欧姆。

- ③ 自谐振频率：几十兆赫兹到几百兆赫兹。电感值越大，其对应的自谐振频率越小。

- ④ 额定电流：几毫安到几十毫安。电感值越大，其对应的额定电流越小。

### 2) 应用特点

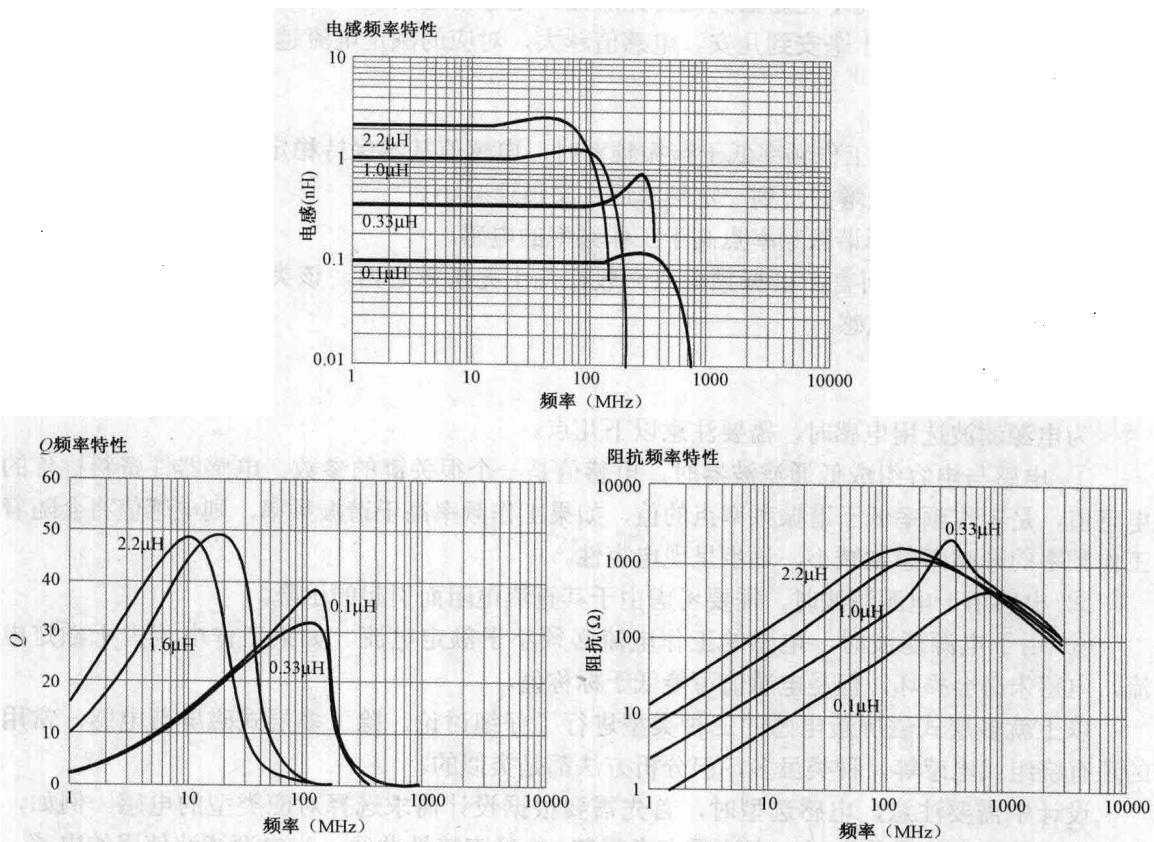

从图 2.28 可知，工作频率低于谐振频率时，电感值基本保持稳定；但工作频率超过谐振频率后，电感值将会先增大，达到一定频率后，将迅速减小。

图 2.28 一般信号用电感电气特性<sup>[13]</sup>

从阻抗频率曲线图可知，工作频率低于谐振频率时，电感器件表现出电感性，阻抗随着频率的升高而增大；当工作频率高于谐振频率时，电感器件表现出电容性，阻抗随着频率的升高而减小。

因此，在应用中，应选择谐振频率点高于工作频率的电感。

对于一般信号用电感而言，谐振频率点一般在几百兆赫兹之内，该类电感也是高速电路设计中最常用的电感。高速设计中的板间互连信号，纹波比板内信号大，可以使用一般信号用电感加以滤波。

设计中需要注意，高频信号用电感和一般信号用电感额定电流都比较小，而直流电阻相对较大，不建议用于电源滤波。

### 3. 电源用电感

电源用电感主要用在电源电路中。

#### 1) 主要参数

① 电感值范围：1~470μH。

② 直流电阻：有多种直流电阻可供选择，电感值越大，其对应的直流电阻也越大。最小的直流电阻一般为几毫欧，大的有几欧姆。

③ 自谐振频率：几十兆赫兹到几百兆赫兹。电感值越大，其对应的自谐振频率越小。

④ 额定电流：几十毫安到几安。电感值越大，对应的额定电流越小。

#### 2) 应用特点

从图 2.29 可知，工作频率低于谐振频率时，电感值基本保持稳定；但工作频率超过谐振频率，电感值将会先增大，到一定频率后，又迅速减小。

在应用中，应选择谐振频率点高于工作频率的电感。

对于电源用电感而言，谐振频率点一般在几十兆赫兹之内，该类电感是高速电路设计中电源滤波最常用的电感。

#### 3) 注意事项

为电源滤波选用电感时，需要注意以下几点。

① 电感与电容组成低通滤波器时，电感值是一个很关键的参数。电感器件资料标称的电感值，是工作频率低于谐振频率点的值，如果工作频率高于谐振频率，则电感值将会随着工作频率的升高而急剧减小，逐步呈现电容性。

② 电感用于电源滤波时，需要考虑由于其直流电阻而引起的压降。

③ 用于电源滤波时，电感的工作电流必须小于额定电流。如果工作电流大于额定电流，电感未必会损坏，但是电感值可能低于标称值。

以上就多层式磁屏蔽电感的三种类型进行了仔细讨论。除了多层式磁屏蔽电感，常用的还有绕组式电感等，种类虽多，但分析方法都是类似的。

设计中需要注意，电感选型时，首先需要根据设计需求选择对应类型的电感。例如，在高速信号线上使用的电感，应该重点考察其  $Q$  频率特性曲线；为电源滤波使用的电感，应重点考察其直流电阻、额定电流等参数。在确定好电感类型后，再根据设计的具体需求，结合电感的特性曲线，在该类型中选择合适的电感。

图 2.29 电源用电感电气特性<sup>[14]</sup>**理解要点：**

- ① 电感与电容构成低通滤波器时，需要注意防止噪声频率点与谐振频率点重合，以免共振。

- ② 电感串联在电源电路中，需考虑电感器件的压降。

- ③ 针对设计需求，选择类型适合的电感。信号线上使用的电感，重点考查其品质因数频率特性曲线；电源电路上使用的电感，应重点考查其直流电阻、额定电流等参数。

## 2.4 磁珠的选型及应用

### 2.4.1 磁珠的滤波机理

磁珠的外形与电感相似，其主要功能是吸收电源、信号上的噪声等干扰。

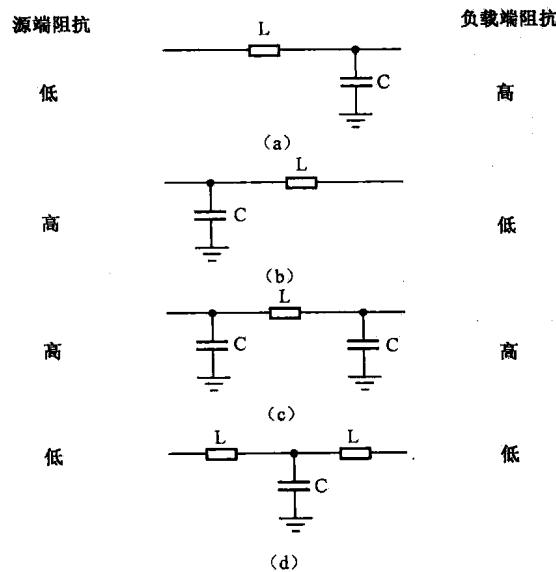

请注意“吸收”这两个字。电容本身可以起到滤波的作用，电感和电容相配合也能起到滤波的作用，但这种滤波，并没有真正将噪声消除。例如，电容的滤波，其原理是在高频时构建一条通到地平面的低阻抗通道，以便将噪声泄放到地平面。而电感和电容配合的滤波，其原理是构建一个低通滤波器，使频段比较低的信号顺利而无衰减地通过，而阻断频段比较高的噪声，低通滤波器对高频段噪声而言，近似于一个极大的电阻，高频段噪声遇到这个极大的电阻，只能被反射回去，基于该原理，应用低通滤波器能有效地保证滤波器后级电路的稳定性。

根据滤波作用原理可知，电容滤波的基础是构建极低阻抗的通道，至于多低的阻抗才

能使单板上绝大多数噪声通过该通道而流回地平面，需要进行大量复杂的电源完整性仿真才能确定。在设计中，一般是采取宁滥勿缺的原则，即布放尽量多的电容，这样做不仅耗费了大量宝贵的 PCB 面积，而且许多电容并没有真正发挥作用，造成无谓的成本上升。而由电感构成的低通滤波，甚至无法将噪声泄放到地平面上，其工作原理是将噪声予以反射，噪声仍然在电路中四处游串；低通滤波的另一个缺陷是，其应用频率范围一般都只能在几十兆赫兹之内，无法有针对性地滤除某些特定频率上的高频噪声。

基于以上讨论，可以看出这两种滤波方式都没有真正地消灭噪声，只是改变了噪声传播的路径。而本小节将要介绍的磁珠，基于的则是完全不同的滤波机理。

磁珠的作用也是滤波，但与电容和电感不同的是，磁珠在一定频带内能反射噪声，在一定频带内还能吸收噪声并转换为热能。

## 2.4.2 高速电路设计中磁珠的选型及其应用要点

在器件资料上，磁珠的参数是其在 100MHz 时的阻抗值。

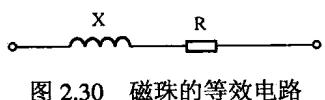

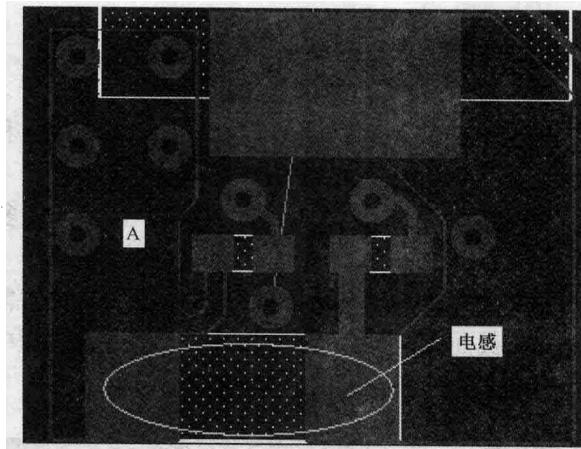

图 2.30 磁珠的等效电路

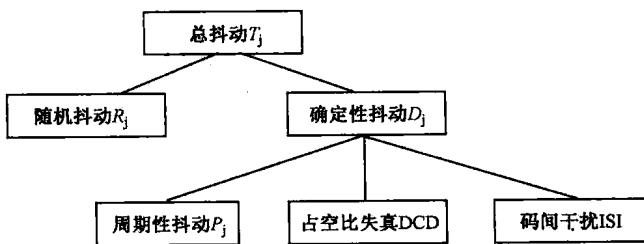

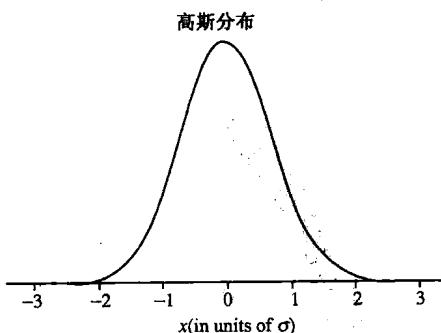

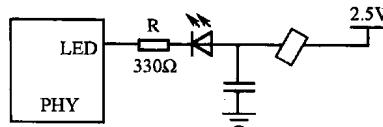

如图 2.30 所示为磁珠的等效电路图。磁珠等效电路的电抗成分以  $X$  表示，电阻成分以  $R$  表示。其整体特性用  $R$  和  $X$  合成的阻抗  $Z$  的频率特性表示<sup>[60]</sup>。

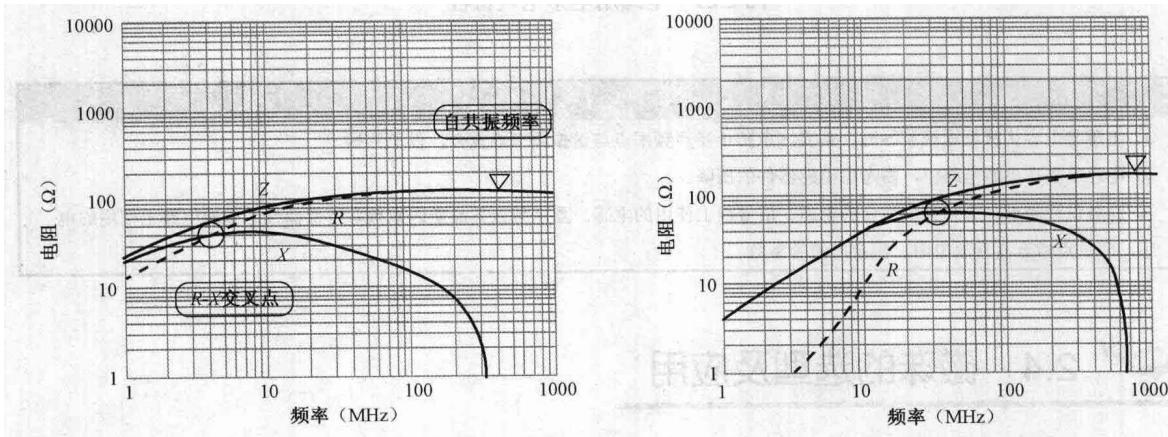

图 2.31 中的特性曲线取自两种磁珠的器件资料。在 100MHz 时这两种器件的阻抗相等，那么这两种器件是否可以完全相互替代？答案是否定的。

图 2.31 两种磁珠的阻抗频率特性曲线<sup>[15]</sup>

磁珠的阻抗  $Z$  由电阻成分  $R$  和电抗成分  $X$  共同决定。在低频段， $X$  起主导作用，磁珠主要体现为电感性，功能是反射噪声；在高频段， $R$  起决定作用，磁珠主要体现为电阻性，功能是吸收噪声并将噪声转换为热。这两种功能的转换点就是曲线上， $R$  和  $X$  值相等处的频率。<sup>[60]</sup>

转换点所在频率以下，磁珠体现电感性，转换点所在频率以上，磁珠体现电阻性。电感性的作用是反射噪声，电阻性的作用是吸收噪声并转化为热能。因此，转换点所在频率越高，磁珠体现电感性的频带越宽，对低频噪声的吸收能力越弱；转换点所在频率越低，磁珠体现电阻性的频带越宽，对低频噪声的吸收能力越强。在磁珠选型时，需要仔细分析电路上信号和噪声所处的频带，所选择的磁珠应满足：电路噪声的频带大于磁珠转换点频率，以便

使磁珠吸收噪声而不是反射噪声；电路信号的频带尽量小于磁珠转换点频率，以防有效信号被磁珠衰减。

对于串联了磁珠的线路，磁珠的转换点频率越低，线路振荡和波形失真就越小；反之则越大。

除了转换点频率外，磁珠选型还需要考虑额定电流、直流电阻和谐振频率（图 2.31 中的自共振频率）等因素。与电感类似，磁珠应用于电源电路滤波时，工作电流不能大于其额定电流；磁珠本身具有直流电阻，当电源电路的电流较大时，还应考虑在磁珠上产生的压降。图 2.31 中，当工作频率高于谐振频率时，磁珠表现出电容性，阻抗迅速减小，因此应选择谐振频率点高的磁珠<sup>[60]</sup>。此处需要特别注意的是，磁珠的转换点频率和谐振频率，在意义上有所不同。

在磁珠的应用中，许多考虑因素与电感相同，本小节不再就磁珠的应用而单独举例。

在高速设计中，磁珠应用的场合越来越多，那么设计中使用磁珠是否会带来副作用？下面就这个问题举一个案例。

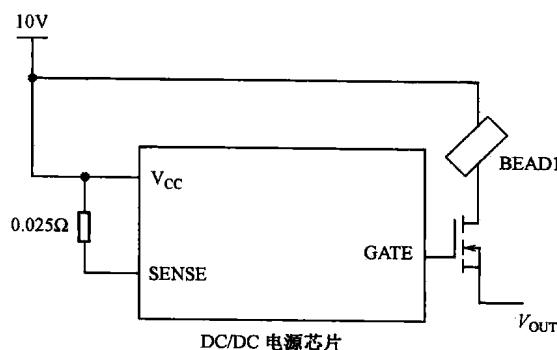

### 【案例 2-15】误用磁珠造成过流保护电路失效

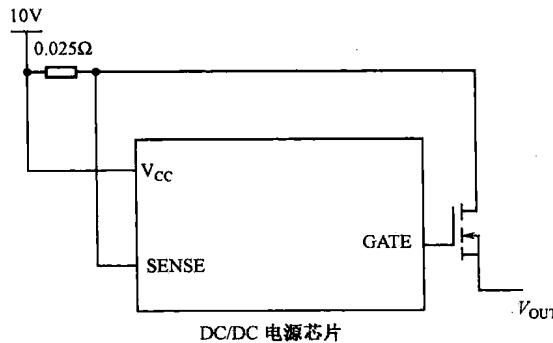

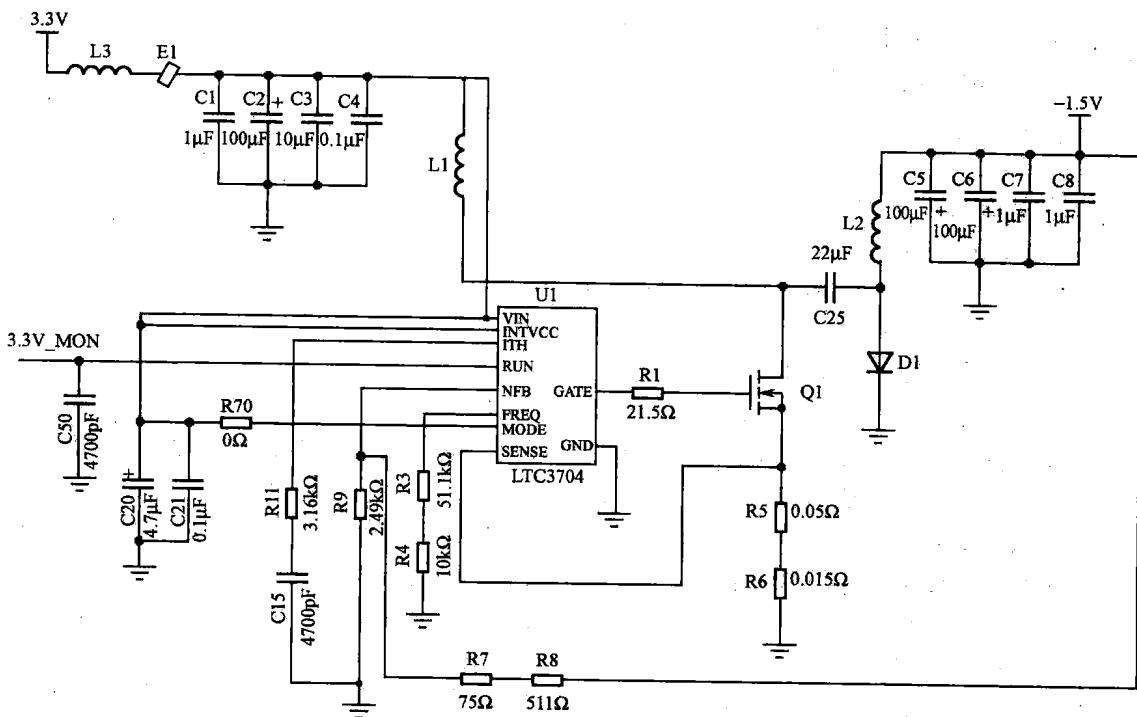

单板上某电源  $V_{OUT}$  由来自背板的电源 10V 通过 DC/DC 电源电路产生，并利用电源芯片的电流监控功能实现过流保护，如图 2.32 所示。在强度测试时发现，即使将  $0.025\Omega$  电阻换为  $0.1\Omega$  电阻，也无法关断 DC/DC 电源芯片的 GATE 输出。

图 2.32 带电流监控功能的 DC/DC 电源电路

### 【讨论】

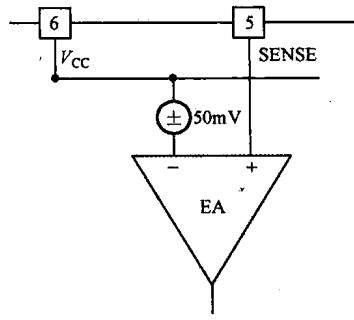

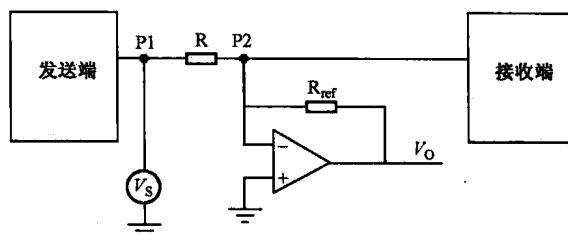

如图 2.33 所示为该 DC/DC 电源芯片的电流监控框图。

该芯片电源监控的原理是利用  $V_{CC}$  引脚和  $SENSE$  引脚之间的电阻压降与芯片内部  $50mV$  电压源相比较的结果，控制 EA（Error Amplifier，偏差放大器）的输出。当电阻压降大于  $50mV$  时，EA 将 GATE 关断。通过电阻  $R$  阻值的选择，可以设置电源电路正常工作时的极限电流流量， $I_{max} = 50mV/R$ 。在本例中，当  $R=0.025\Omega$  时  $I_{max}=2A$ ；强度测试中， $R=0.1\Omega$  时， $I_{max}=0.5A$ 。对  $V_{OUT}$  进行电流测试发现，单板稳定工作时，10V 电源上的电流为 0.8A，电源芯片为何没有检测到过流？

图 2.33 DC/DC 电源芯片电流监控框图

仔细查看原理图，发现电流监控和  $V_{OUT}$  的产生，二者实际上走了两条不同的路径，即 10V 电源进入单板后，分开两路，一路通过电阻连接到电源芯片的 SENSE 引脚，一路通过 BEAD1 与 MOSFET 相连后产生  $V_{OUT}$ 。在这两路中，第一条路径是不耗电流的，第二条路径才是真正需要被监控的。但在本设计中，实际得到监控的是不耗电流的第一条路径，所以在强度测试中，即便将  $R$  改为  $0.1\Omega$ ，也不会报警过流。

在电源电路中，设计者往往喜欢串接磁珠以实现滤波，这几乎成了最常规的设计方法，因此往往不加仔细思考。但从这个案例可以看出，过度地使用磁珠也会带来副作用，而且问题往往比较隐蔽。

在改板设计中，将磁珠 BEAD1 去掉，电路修改为图 2.34，过流保护功能得以实现。

图 2.34 改板后的 DC/DC 电源电路

#### 理解要点：

- ① 磁珠的转换点频率越低，线路振荡和波形失真越小，反之则越大。

- ② 磁珠的工作电流不能大于其额定电流，设计中需考虑到由于直流电阻的存在而造成的压降。

- ③ 当工作频率高于谐振频率时，磁珠表现出电容性。

- ④ 磁珠的转换点频率和谐振频率，在意义上有所不同。

### 2.4.3 磁珠和电感的比较

#### 1. 磁珠与电感的不同点

磁珠与电感不仅在外形上相似，在功能上也存在很多相似之处，甚至在许多场合，磁珠

和电感能相互替代。但是磁珠和电感是否完全等同呢？以下就几个方面对两者进行比较。

(1) 电感和磁珠都可以用于滤波，但是机理不一样。电感滤波是将电能转换为磁能，磁能将通过两种方式影响电路：一种方式是重新转换回电能，表现为噪声；一种方式是向外部辐射，表现为 EMI（电磁干扰）。而磁珠是将电能转换为热能，不会对电路构成二次干扰。

(2) 电感在低频段滤波性能较好，但在 50MHz 以上的频段滤波性能较差；磁珠利用其电阻成分能充分地吸收高频噪声，并将之转换为热能以达到彻底消除高频噪声的目的。

(3) 从 EMC（电磁兼容）的层面说，由于磁珠能将高频噪声转换为热能，因此具有非常好的抗辐射功能，是常用的抗 EMI 器件，常应用于用户接口信号线滤波、单板上的高速时钟器件的电源滤波等。

(4) 电感和电容构成低通滤波器时，由于电感和电容都是储能器件，因此两者的配合可能产生自激；磁珠是耗能器件，与电容协同工作时，不会产生自激。

(5) 一般而言，电源用电感的额定电流相对较大，因此，电感常用于需要通大电流的电源电路上，如用于电源模块滤波；而磁珠一般仅用于芯片级电源滤波（不过，目前市场上已经出现了大额定电流的磁珠）。

(6) 磁珠和电感都具有直流电阻，磁珠的直流电阻相对于同样滤波性能的电感更小一些，因此用于电源滤波时，磁珠上的压降更小。

## 2. 磁珠与电感的共同点

(1) 额定电流。当电感的工作电流超过其额定电流时，电感值将迅速减小，但电感器件未必被损坏；而磁珠的工作电流超过其额定电流时，将会对磁珠造成损伤。

(2) 直流电阻。用于电源线路时，线路上存在一定的电流，如果电感或磁珠本身的直流电阻较大，则会产生一定压降。因此选型中，都要求选择直流电阻小的器件。

(3) 频率特性曲线。电感和磁珠的厂家资料都附有器件频率特性曲线图。在选型中，需要仔细参考这些曲线，以选择合适的器件。

# 第3章 高速电路中的逻辑器件选型及高速逻辑电平应用

电路设计离不开与门、非门、驱动器等逻辑器件，对逻辑器件的熟练应用是硬件工程师的一项基本技能。

本章将重点讨论逻辑器件的选型和应用技巧。

## 3.1 与逻辑器件相关的经典案例

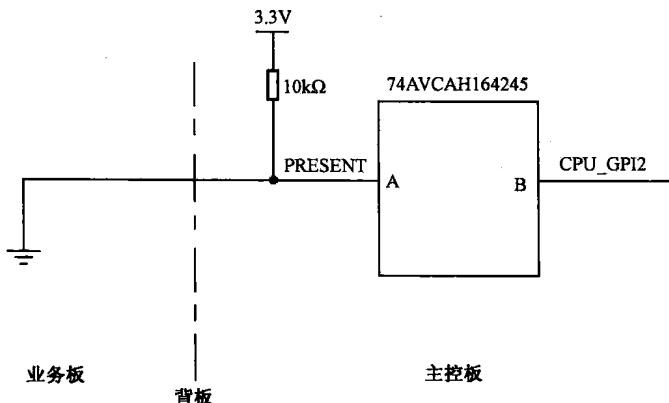

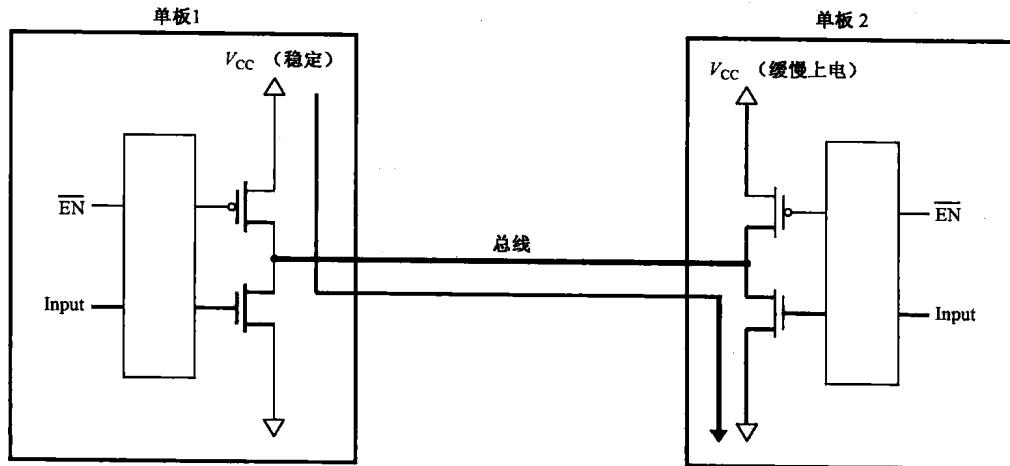

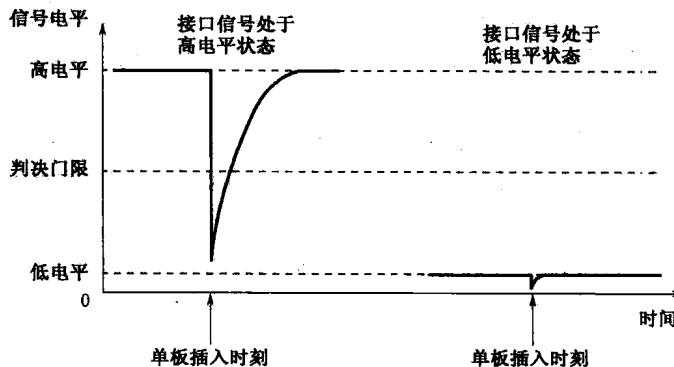

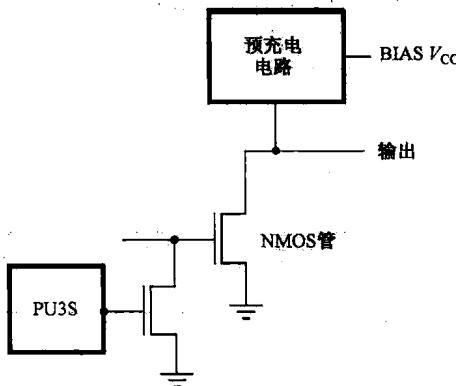

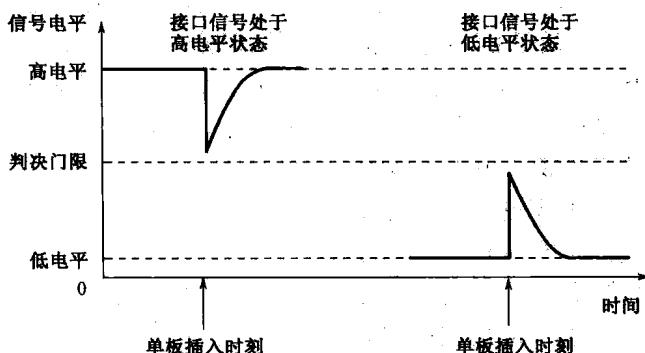

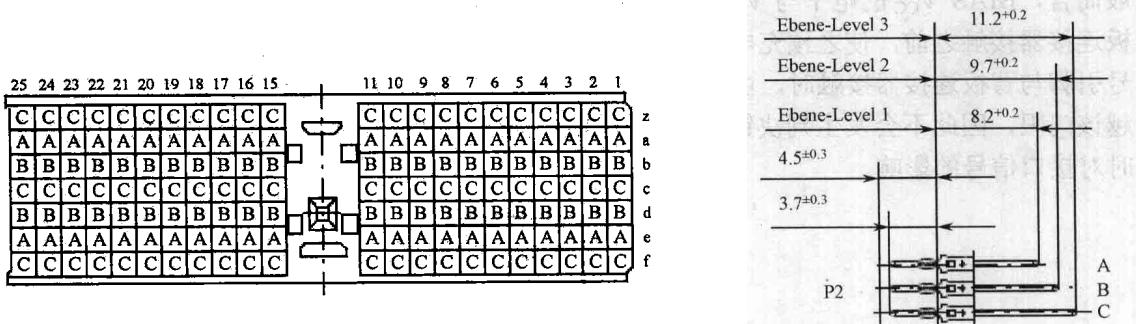

### 【案例 3-1】 逻辑器件输入端上拉太弱造成带电插拔监测功能失效

某产品支持业务板的带电插拔，主控板通过业务板的在位信号判断业务板插入或拔出的状态。测试时发现，主控板能检测到业务板的插入，但有时，不能检测到业务板的拔出。

#### 【讨论】

该产品业务板热插拔监控电路如图 3.1 所示。

图 3.1 业务板热插拔监控电路

业务板的在位信号（PRESENT）通过背板连接到主控板逻辑驱动器件 74AVCAH164245 的输入端，在业务板上，该信号直接接地，在主控板上，该信号通过  $10\text{k}\Omega$  电阻上拉到 3.3V，PRESENT 信号经驱动后得到 CPU\_GPI2 信号，连接到 CPU 的 GPIO（通用输入/输出接口）。当业务板插入时，在位信号变为低电平，CPU\_GPI2 输出低电平，通知 CPU，该槽位的业务板已插入；当业务板拔出时，在位信号变为高电平，CPU\_GPI2 输出高电平，通知 CPU，该槽位的业务板已拔出。

业务板插入时，测量 CPU\_GPI2 信号，测得低电平，因此主控板能检测到业务板的插

入事件；业务板拔出时，测量 CPU\_GPI2 信号多次，发现有时该信号不能变为高电平，导致主控板无法识别业务板的拔出，此时，在主控板上同时测量 PRESENT 信号，信号状态正确，即拔出业务板后，PRESENT 信号能迅速变为高电平。因此问题定位为，当 74AVCAH164245 的输入端发生电平由低到高的转换时，输出端不能产生相应的电平变化。

74AVCAH164245 是一种具有总线保持（Bus Hold）功能的驱动器。查阅器件资料，该器件对电平翻转时的电流有一定要求，由参数  $I_{BHLO}$  和  $I_{BHHO}$  定义。

$I_{BHLO}$  的最小值为  $525\mu A$ ，指当电平发生由低到高的翻转时，驱动器应至少吸收电流  $525\mu A$ （接收端电流方向为输入，因此是正电流）； $I_{BHHO}$  的最小值为  $-525\mu A$ ，指当电平发生由高到低的翻转时，驱动器应至少输出电流  $525\mu A$ （接收端电流方向为输出，因此是负电流）。

当业务板插入时，逻辑器件 74AVCAH164245 输入端的电平发生由高到低的翻转，电流从逻辑器件流向地平面，因此逻辑器件能准确识别该电平变化，驱动 CPU\_GPI2 为低电平。当业务板拔出时，逻辑器件输入端的电平发生由低到高的翻转，电流由  $3.3V$  电源平面经  $10k\Omega$  电阻流入逻辑器件输入端，提供的电流为  $3.3V/10k\Omega=330\mu A$ ，达不到  $I_{BHLO}$  最小值的要求，因此逻辑器件无法准确识别输入电平的翻转，也就不可能将 CPU\_GPI2 信号驱动为高电平。

在改板设计中，将上拉电阻阻值由  $10k\Omega$  改为  $1k\Omega$ ，热插拔监控功能恢复正常。

### 【拓展】

本案例中的逻辑器件具有总线保持功能，那么该功能有何实际意义？

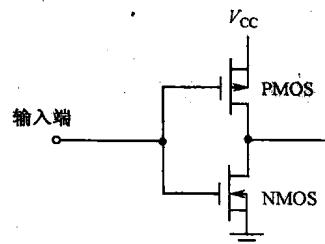

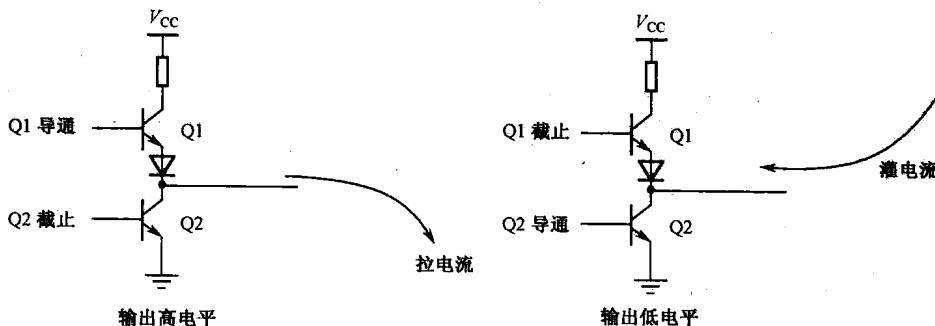

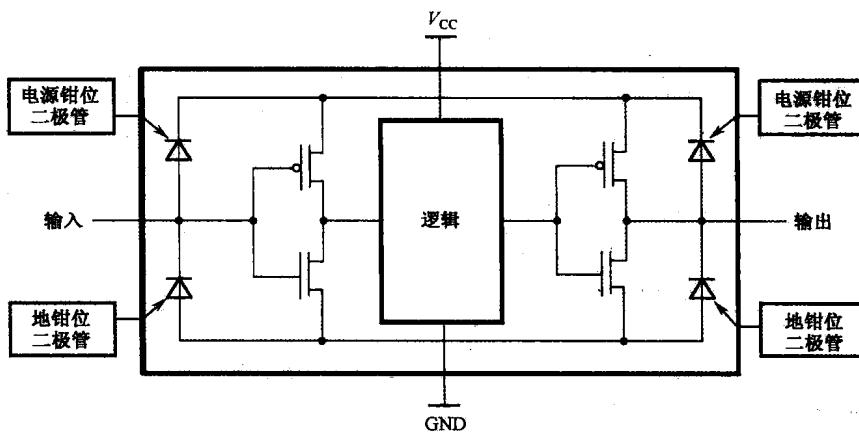

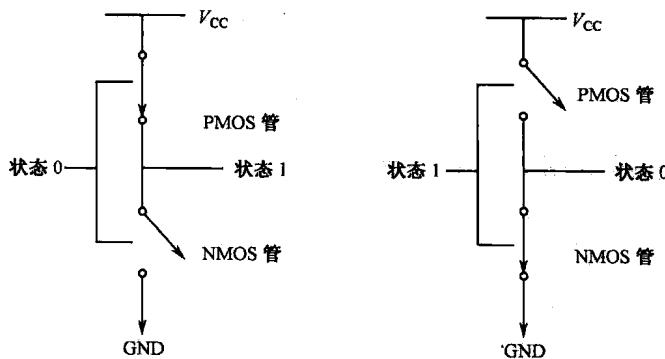

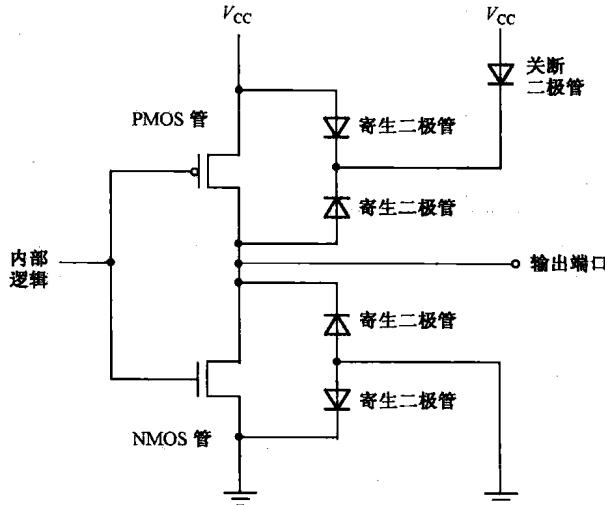

常用的逻辑器件，如 74LV、74AC、74AHC、74HC 等系列，都属于 CMOS 器件。CMOS 器件的输入端由栅极连接在一起的一对 PMOS 和 NMOS 构成，如图 3.2 所示。当输入低电平时，PMOS 导通而 NMOS 关闭，输入高电平时，PMOS 关闭而 NMOS 导通，在理想状况下，两个 MOS 管不会同时导通。

图 3.2 CMOS 器件输入端

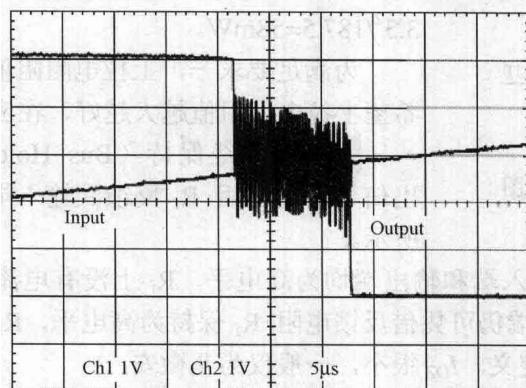

但是，在输入信号的高电平  $V_{IH}$  和低电平  $V_{IL}$  之间，存在一段区间，称为非稳态区间。例如，74AVCAH164245 的  $V_{IH(min)}$  为  $2V$ ， $V_{IL(max)}$  为  $0.8V$ ，因此，该器件的非稳态区间为  $0.8\sim 2V$ 。在这段区间内，PMOS 和 NMOS 都将部分地导通，以致输出产生振荡。

图 3.3 CMOS 器件输入端处于非稳态时，输出端发生振荡<sup>[25]</sup>

图 3.3 是 CMOS 器件输入端处于非稳态时，输出端发生的振荡波形。

有三种情况可能导致输入端处于非稳态：

**情况一**，输入信号的边沿斜率不可能是理想的  $90^\circ$ ，必然会有一段时间处于非稳态，对于这种情况，只能通过提高输入信号边沿爬升速率来解决；

**情况二**，发生总线冲突，导致在同一个信号上，出现了多个驱动源。这可以通过改进设计以避免这种情况的发生；

**情况三**，输入信号没有驱动源，即完全浮空的情况。

第一种情况是必然发生的，第二种情况可以避免，而第三种情况则常用四种解决方法<sup>[25]</sup>。

以下讨论情况三的解决方法：

**方法一**当输入信号没有驱动源时，使逻辑器件的输出使能引脚 OE# 处于无效状态，以关闭与该输入信号对应的输出。

**方法二**总线上挂有多个器件，且这些器件可以均等地申请总线的控制权。在这种情况下，使最后一个控制总线的器件在工作完成后，仍然保持对总线的驱动，直到下一个器件申请总线的控制权，才释放出总线。这使得在任何时刻，总线上都存在一个器件作为总线驱动者，任何一个接收器件的输入端都不会浮空。PCI 总线即采用了这种机制。

**方法三**上拉电阻。在逻辑器件的输入引脚上增加一个上拉到电源  $V_{CC}$  的电阻，当输入端失去驱动源时，通过该上拉电阻， $V_{CC}$  可直接作为输入端的驱动源。采用这种方法时，需要注意满足以下两个要求：

**要求一**，信号的上升沿爬升时间  $t_r$  应满足逻辑器件的要求。上拉电阻  $R_P$  的计算公式为：

$$R_P = \frac{t_r}{2.2 \times C_s \times n} \quad (3.1) [25]$$

式中  $C_s$ ——输入引脚的寄生电容；

$n$ ——该信号线上并联器件的数目。

例如，某逻辑器件的上升沿爬升速率要求为  $0.2V/ns$ ，电源  $V_{CC}$  为  $3.3V$ ，则  $t_r$  应不大于  $16.5ns$ ，假设  $C_s=20pF$ ,  $n=2$ ，则该逻辑器件的输入端上拉电阻  $R_P$  计算结果如下：

$$R_P = 16.5ns / (2.2 \times 20pF \times 2) = 187.5\Omega$$

即只有当上拉电阻阻值小于  $187.5\Omega$  时，才能满足该器件的上升沿爬升速率要求。

**要求二**，上拉电阻消耗的功率应尽量小。在上例中，上拉电阻上的功耗为  $3.3^2 / 187.5 = 58mW$ 。

图 3.4 总线保持原理框图

为满足要求一，上拉电阻阻值越小越好，而要求二则希望上拉电阻阻值越大越好，在应用中应折中考虑。

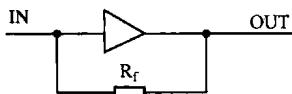

**方法四**总线保持 (Bus Hold)。其实现原理是将输出信号通过电阻  $R_f$  反馈回输入端，功能模块图如图 3.4 所示。

假设初始状态为，输入端和输出端均为高电平， $R_f$  上没有电流流过。此时如果输入端的驱动源停止驱动，输入端仍可凭借反馈电阻  $R_f$  保持为高电平， $R_f$  上流过电流为漏电流，在器件资料上由参数  $I_{OZ}$  定义， $I_{OZ}$  很小，一般仅为几微安。

以上针对情况三提出了四种方法。这四种方法都是电路中常见的设计方法。**方法一**需增加 OE# 信号，并需要得到外部逻辑电路的配合；**方法二**需得到总线协议的支持；**方法三**

需外加上拉电阻，且阻值的选择需根据信号变化沿速率和功耗做出取舍；方法四最简单，无需外加元件和辅助电路。

当然在使用具有总线保持功能的器件时，应避免出现本案例所遇到的情况。

## 3.2 逻辑器件应用要点

### 3.2.1 逻辑器件概要

#### 1. TTL、CMOS、LVTTL、LVCMOS 逻辑电平介绍及互连

逻辑器件的选型首先是逻辑电平的选择，在传统的单板设计中，TTL 和 CMOS 逻辑电平被广泛应用，是数字电路设计中最常见的两种逻辑电平，LVTTL 和 LVCMOS 是它们的低电平版本，其他的高速电平大多都衍生自 TTL 和 CMOS。

TTL 指晶体管—晶体管逻辑，由于晶体管是流控器件，且输入电阻较小，因此 TTL 电平的器件速度快，但功耗较大；CMOS 是 MOS 管逻辑，由于 MOS 管是压控器件，且输入电阻极大，因此 CMOS 电平的器件速度较慢，但功耗较小，同时由于 CMOS 器件输入阻抗很大，外界微小的干扰就可能引起电平的翻转，因此 CMOS 器件上未使用的输入引脚应做上下拉处理，不能浮空。

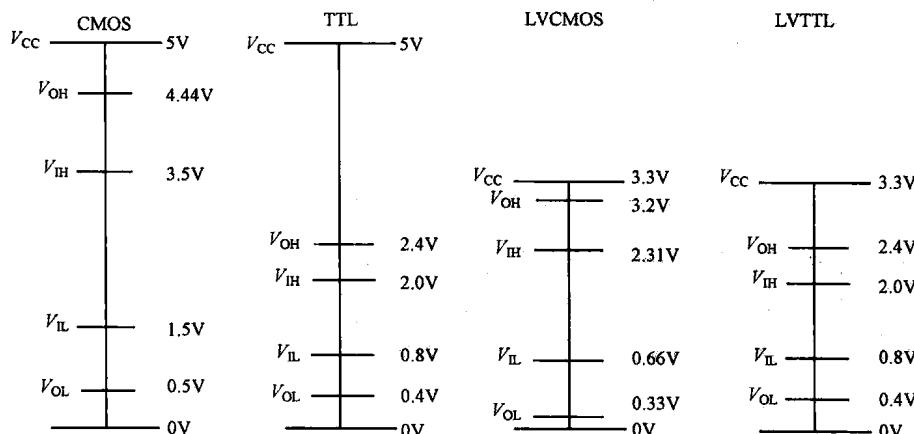

现实中的信号是连续的模拟信号，而数字信号只有“1”和“0”两种逻辑状态，需使用阈值来定义信号的逻辑状态。下面以图 3.5 为例，说明信号的逻辑电平定义。

图 3.5 逻辑电平阈值示例

在图 3.5 中，对每种逻辑电平都定义了四个阈值，即  $V_{O_{\text{H}}}$ 、 $V_{O_{\text{L}}}$ 、 $V_{I_{\text{H}}}$ 、 $V_{I_{\text{L}}}$ 。

当逻辑器件输出高电平时，电平的幅值应高于  $V_{O_{\text{H}}}$ ，即  $V_{O_{\text{H}}}$  为输出高电平的最小值；

当逻辑器件输出低电平时，电平的幅值应低于  $V_{O_{\text{L}}}$ ，即  $V_{O_{\text{L}}}$  为输出低电平的最大值；

当逻辑器件输入高电平时，电平的幅值应高于  $V_{I_{\text{H}}}$ ，即  $V_{I_{\text{H}}}$  为输入高电平的最小值。

当逻辑器件输入低电平时，电平的幅值应低于  $V_{I_{\text{L}}}$ ，即  $V_{I_{\text{L}}}$  为输入低电平的最大值。

从图 3.5 可以发现，各逻辑电平的阈值并不相同，因此相互间并非可以直接互连。只有同时满足以下条件时，不同逻辑电平的器件才能直接互连。

**条件一**, 发送方  $V_{OH}$  大于接收方  $V_{IH}$ , 且提供一定的噪声容限。

**条件二**, 发送方  $V_{OL}$  小于接收方  $V_{IL}$ , 且提供一定的噪声容限。

例如, 当 LVTTL 电平的器件能承受 5V 信号的输入时, 可以和 TTL 电平的器件直接互连; CMOS 器件作为发送方, TTL 器件作为接收方, 两者可以互连; 但 TTL 器件作为发送方, CMOS 器件作为接收方时, 则不能互连。

相同电平的逻辑器件之间, 能自然满足以上两个条件, 因此可以直接互连。

需注意, 图 3.5 只是一个示意图, 对于不同型号的逻辑器件, 即使使用同种逻辑电平, 阈值也不一定相同, 设计中应查阅器件资料以获得各项阈值参数。

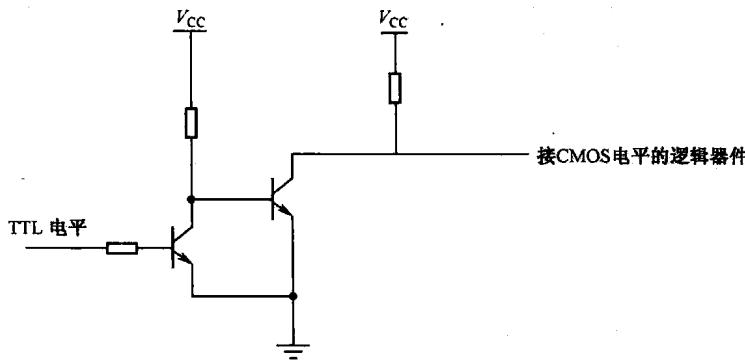

对于电平不同, 且不能满足直接互连条件的逻辑器件, 可采用以下方法实现互连。

**方法一**, 使用电平转换芯片。例如, 74ACT16245, 其输入端为 TTL 电平, 输出端为 CMOS 电平, 因此支持 TTL 到 CMOS 电平的转换。当存在大量信号需做电平转换时, 可采用这种方法。

**方法二**, 使用 OC (集电极开路) 门或 OD (漏极开路) 门实现逻辑电平的转换。如图 3.6 所示, 通过 OC 门电路, TTL 器件可与 CMOS 器件相连。OC 或 OD 门还常被用于低逻辑电平驱动高逻辑电平的场合。

图 3.6 利用 OC 门实现逻辑电平的转换

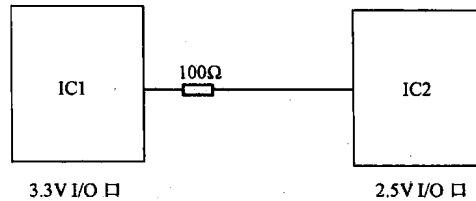

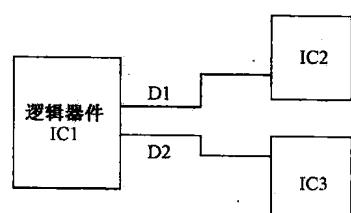

**方法三**, 高逻辑电平驱动低逻辑电平时, 可串联  $50\sim330\Omega$  电阻实现电平的转换。如图 3.7 所示, IC1 的 I/O 接口是 3.3V 电平, IC2 的 I/O 接口是 2.5V 电平, 可通过串联电阻实现两者的互连, 串联电阻的阻值需根据 I/O 口动态电流进行计算。

图 3.7 串联电阻实现逻辑电平的转换

电路设计时, 通过 JTAG 接口 (一种标准的接口, 将在第 8 章进行详细介绍), 可将单板上的芯片连成一条链路。如果遇到某些芯片的 JTAG 接口逻辑电平与其他芯片不同, 可利用方法二和方法三实现链路的连接。

逻辑器件互连时, 除考虑电平转换之外, 还应考虑器件的驱动能力、时延特性等, 后

续章节将有对应内容的讨论。

## 2. 逻辑器件分类

电路设计中，74 族逻辑器件的厂家有 TI、NXP、Fairchild 等。

根据工艺不同，逻辑器件可分为三类：Bipolar（双极型），CMOS（互补金属氧化物半导体）和 BiCMOS（Bipolar CMOS）。

Bipolar 是由双极型晶体管组成的集成电路，如 TTL 电路就属于 Bipolar，特点是速度快，驱动能力强，但功耗较大。

CMOS 是由场效应管构成的集成电路，特点是功耗低，集成度高，但驱动能力和速度比 Bipolar 差。

随着高速电路的发展，单板密度越来越高，功耗越来越大，器件的工作速度也越来越快，Bipolar 和 CMOS 已逐渐不能满足设计的要求，需要采用新的工艺——BiCMOS。

BiCMOS 主要具有以下两种优势：

(1) BiCMOS 以 CMOS 工艺为主，CMOS 电路充当高集成度和低功耗的电路核心部分，用 Bipolar 电路充当输入/输出接口部分，因此可以充分发挥 Bipolar 和 CMOS 的优势，同时具有速度高、驱动能力强和功耗低、集成度高的优点。

(2) 随着工作温度和工作电压的变化，CMOS 器件和 Bipolar 器件的许多特性都会发生变化，且对于许多特性参数，CMOS 和 Bipolar 器件的变化方向是相反的。例如，传输延时参数，随着温度的降低，CMOS 器件的传输延时减小，而 Bipolar 器件的传输延时增大；随着温度的升高，CMOS 器件的传输延时增大，Bipolar 器件的传输延时虽然也增大，但增加的幅度小于 CMOS 器件。BiCMOS 工艺将 Bipolar 和 CMOS 这两种具有互补特性的工艺结合在一起，使得器件参数随工作电压和工作温度的变化曲线较平缓，提高了器件的性能。

电路设计中常用的 74 族逻辑器件，根据制造工艺、I/O 接口结构的不同，可分为多种系列<sup>[26]</sup>：

ABT：先进 BiCMOS 技术（Advanced BiCMOS Technology）；

AC/ACT：先进 CMOS 逻辑（Advanced CMOS Logic）；

AHC/AHCT：先进高速 CMOS 逻辑（Advanced High-Speed CMOS Logic）；

ALS：先进低功耗肖特基逻辑（Advanced Low-Power Schottky Logic）；

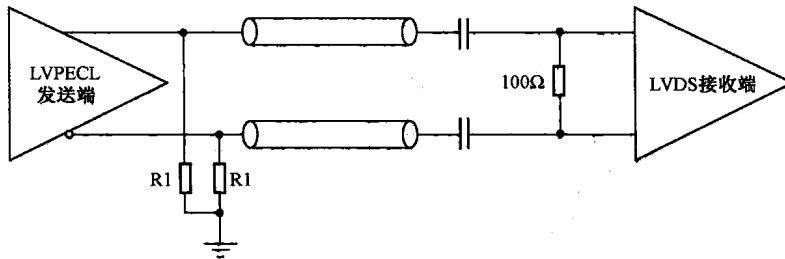

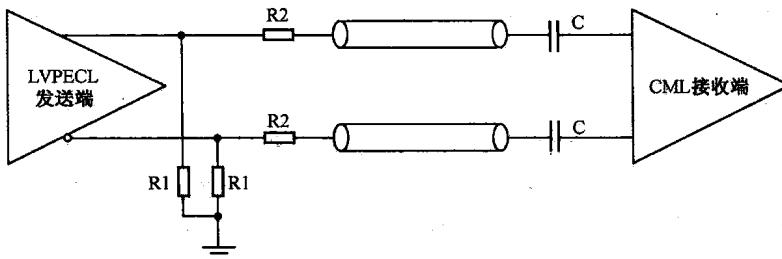

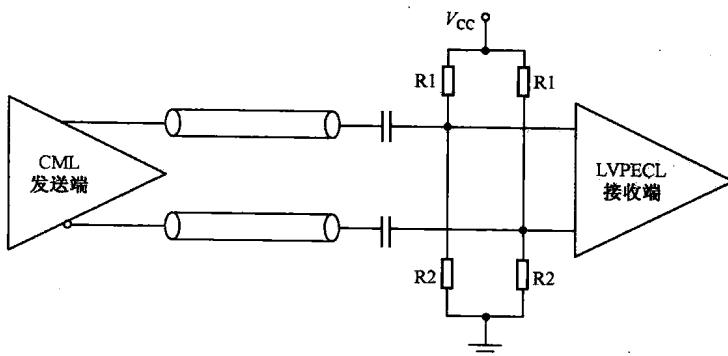

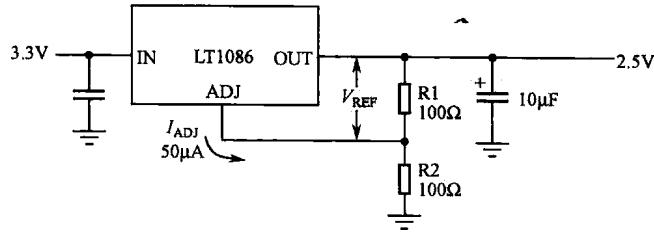

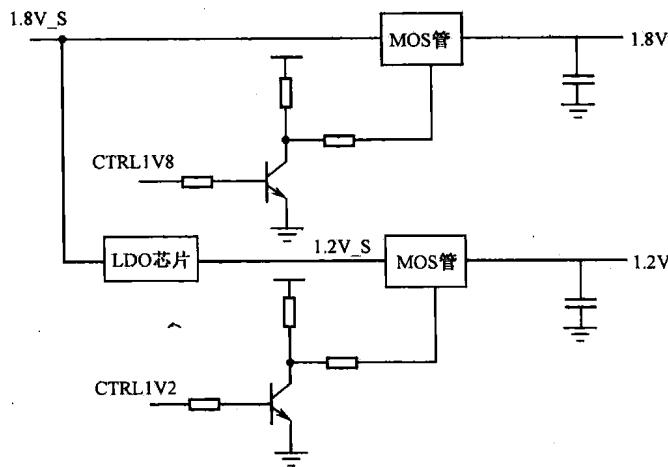

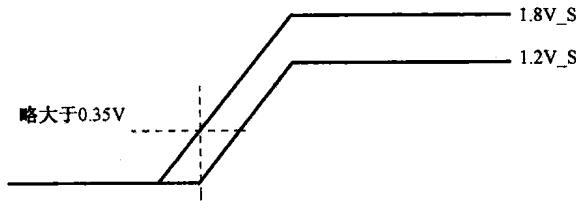

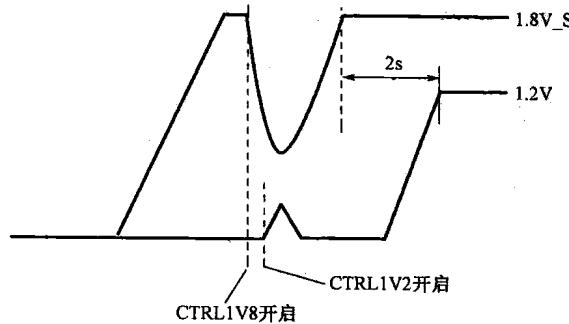

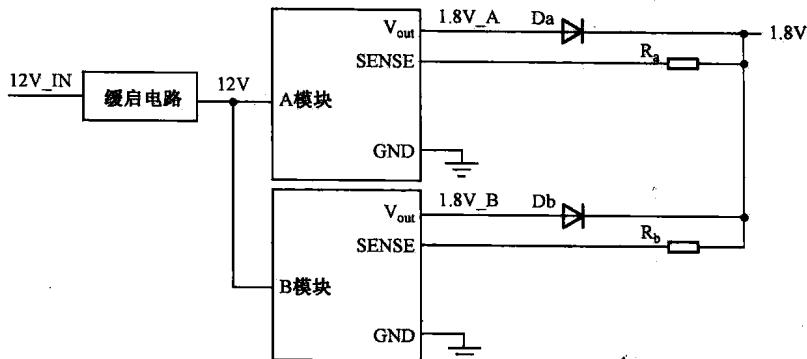

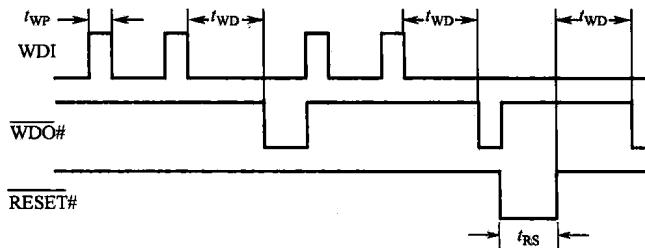

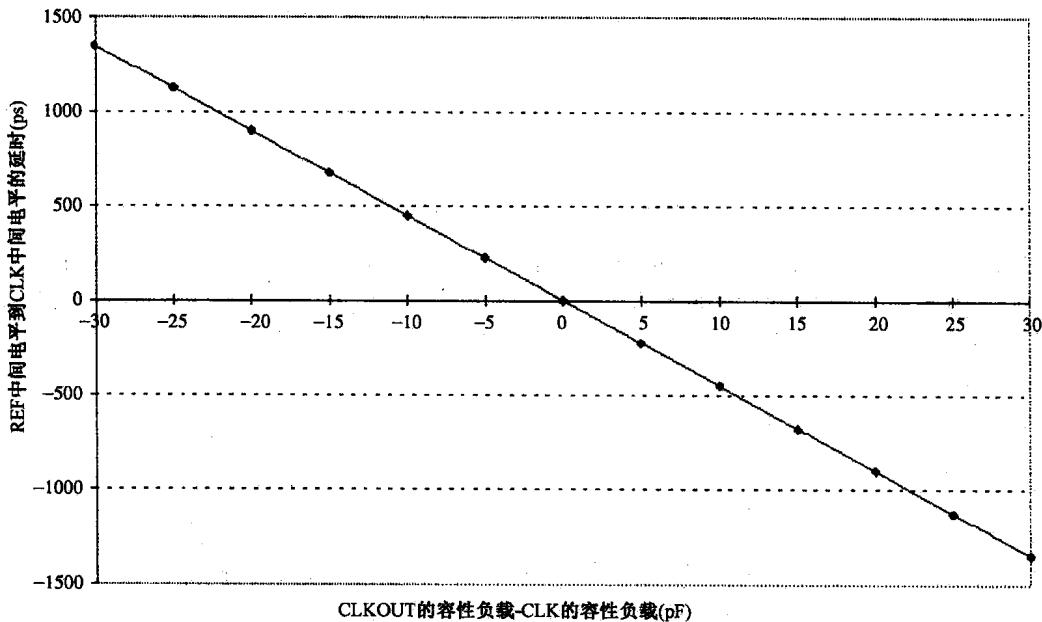

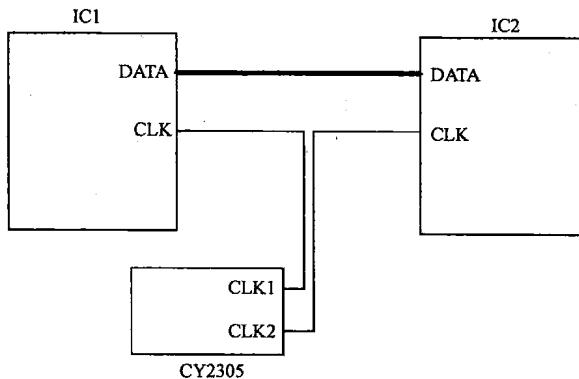

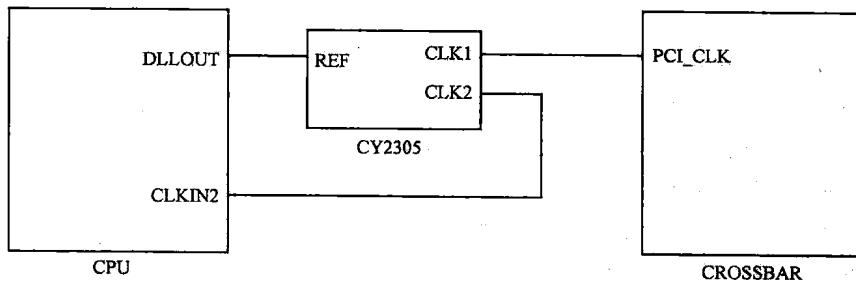

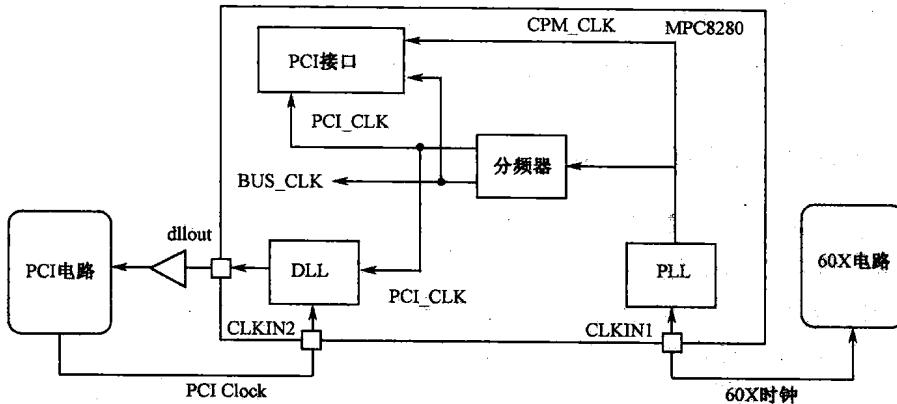

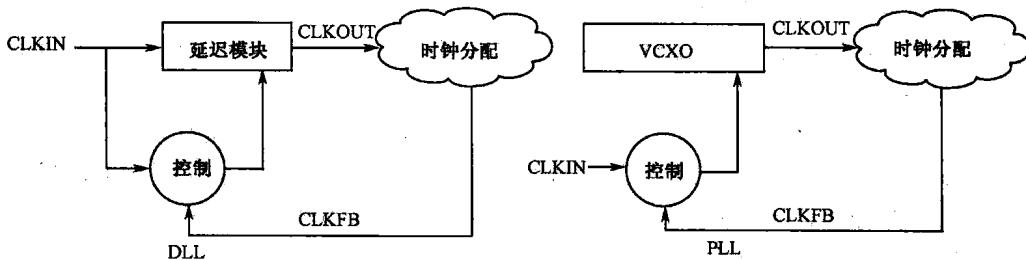

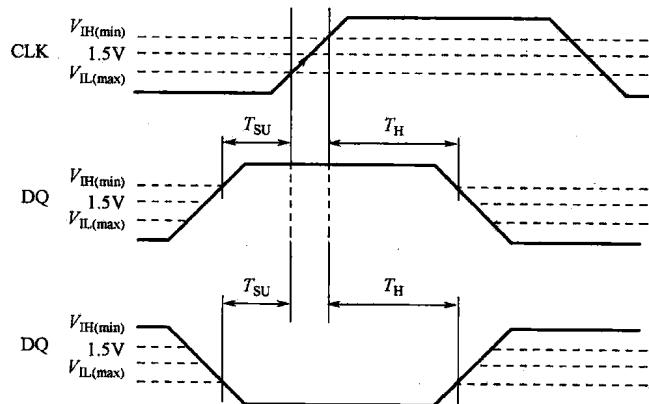

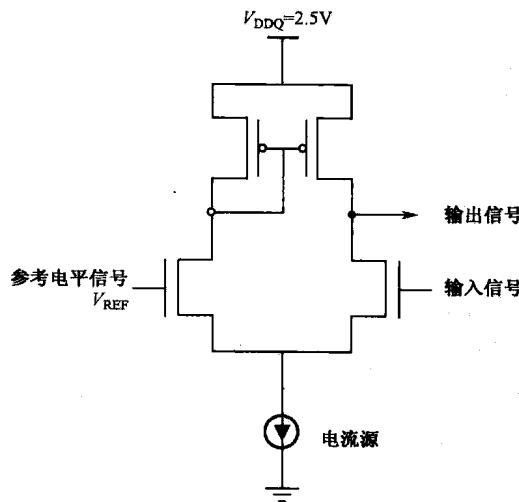

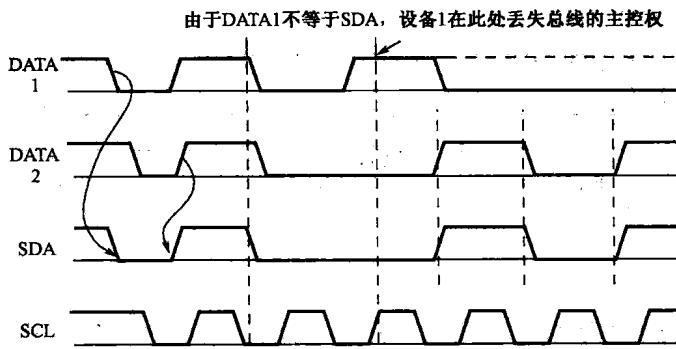

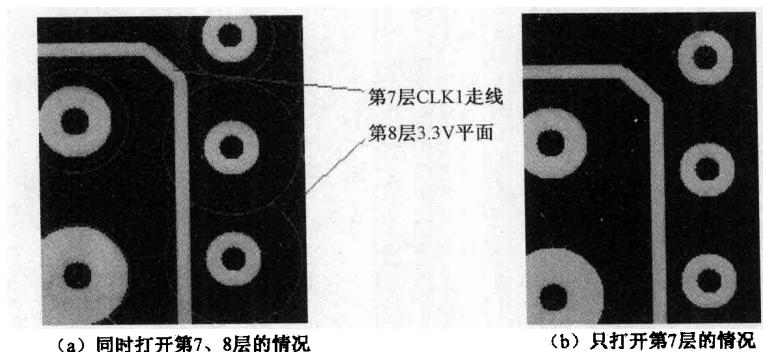

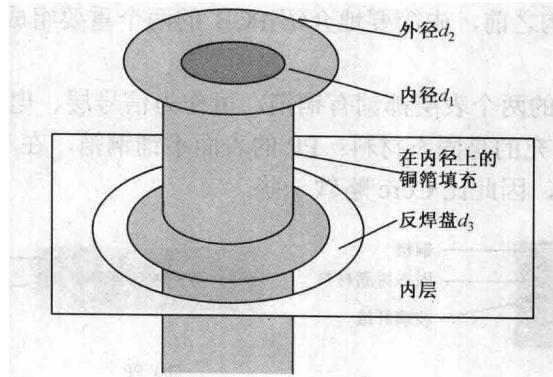

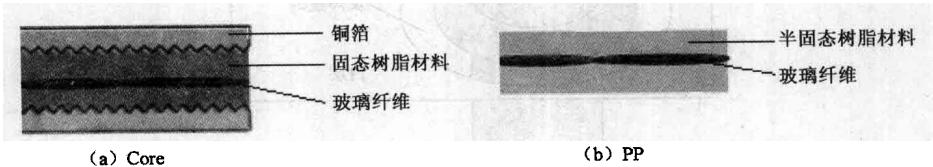

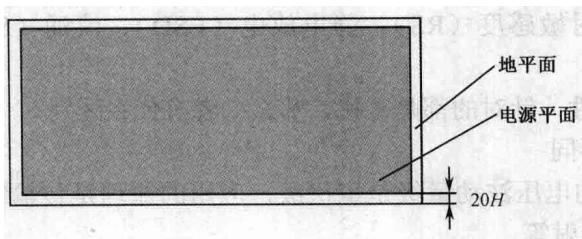

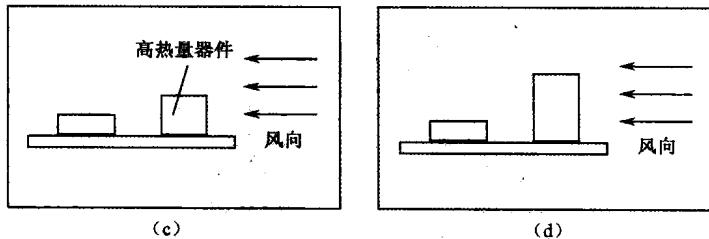

ALVC：先进低电压 CMOS 技术（Advanced Low-Voltage CMOS Technology）；